# 28F020 2048K (256K x 8) FLASH MEMORY

SmartDie Product Specification

- Flash Electrical Chip Erase — 2 Second Typical Chip Erase

- Quick-Pulse Programming Algorithm —10 μs Typical Byte Program

- 4 Second Chip Program

- 100K Erase/Program Cycles Typical

- 12.0V ±5% Vpp

- High-Performance Read - 90 ns Access Time

- **CMOS Low Power Consumption**

- 10 mA Typical Active Current

- **—50**  $\mu$ **A** Typical Standby Current

- 0W Data Retention Power

- Integrated Program/Erase Stop Timer

- Command Register Architecture for Microprocessor/Microcontroller Compatible Write Interface

- Noise Immunity Features

- ± 10% V<sub>CC</sub> Tolerance

Maximum Latch-Up Immunity through EPI Processing

- ETOX™ III Nonvolatile Flash **Technology**

- EPROM-Compatible Process Base

- High-Volume Manufacturing **Experience**

- Intel SmartDie Product

- Full AC/DC Testing at Die Level

- -0 °Cb +80°C (Junction) **Temperature Range**

- Available in 90 ns Access Time Only

NOTICE: This document contains preliminary information on new products in production. It is valid for the devices indicated in the revision history. This specification is subject to change without notice.

REFERENCE INFORMATION: The information in this document is provided as a supplement to the Standard Package Data Sheet on a specific product. Please reference the Standard Package Data Sheet/Book (Order No. 290245) for additional product information and specifications not found in this document.

28F020 2048K (256K x 8) Flash Memory Die Photo

# 1.0 DIE SPECIFICATIONS

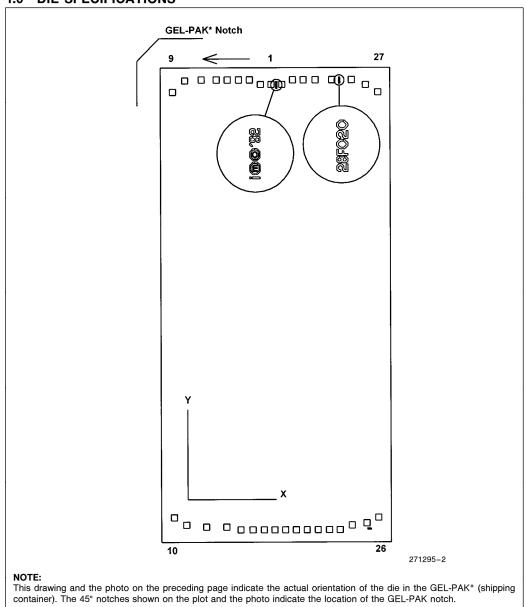

Figure 1. 28F020 2048K (256K x 8) Flash Memory Die/Bond Pad Layout

PRELIMINARY 3

# 1.1 Pad Description

Table 1. 28F020 2048K (256K x 8) Flash Memory Bond Pad Center Data

|     | Signal          | Pad Center         |        |           |       |  |

|-----|-----------------|--------------------|--------|-----------|-------|--|

| Pad |                 | (Mils = 0.001 in.) |        | (Microns) |       |  |

|     |                 | Х                  | Υ      | х         | Υ     |  |

| 001 | V <sub>CC</sub> | -2.7               | 147.0  | -68       | 3735  |  |

| 002 | $V_{PP}$        | -9.9               | 147.0  | -253      | 3735  |  |

| 003 | A16             | -17.3              | 150.3  | -439      | 3817  |  |

| 004 | A15             | -24.8              | 150.3  | -629      | 3817  |  |

| 005 | A12             | -32.5              | 150.3  | -825      | 3817  |  |

| 006 | A7              | -39.9              | 150.3  | -1012     | 3817  |  |

| 007 | A6              | -50.1              | 150.3  | -1272     | 3817  |  |

| 800 | A5              | -61.4              | 149.7  | -1560     | 3801  |  |

| 009 | A4              | -69.7              | 141.9  | -1770     | 3604  |  |

| 010 | A3              | -69.5              | -142.1 | -1764     | -3610 |  |

| 011 | A2              | -61.0              | -147.1 | -1550     | -3736 |  |

| 012 | A1              | -47.4              | -148.5 | -1205     | -3771 |  |

| 013 | A0              | -33.9              | -148.5 | -860      | -3771 |  |

| 014 | DQ0             | -24.2              | -150.3 | -615      | -3817 |  |

| 015 | DQ1             | <b>-15.9</b>       | -150.3 | -404      | -3817 |  |

| 016 | DQ2             | -8.4               | -150.3 | -212      | -3817 |  |

| 017 | V <sub>SS</sub> | -1.0               | -150.3 | -26       | -3817 |  |

| 018 | V <sub>SS</sub> | 6.3                | -150.3 | 159       | -3817 |  |

| 019 | DQ3             | 13.5               | -150.3 | 344       | -3817 |  |

| 020 | DQ4             | 20.9               | -150.3 | 530       | -3817 |  |

| 021 | DQ5             | 28.4               | -150.3 | 720       | -3817 |  |

| 022 | DQ6             | 36.1               | -150.3 | 917       | -3817 |  |

| 023 | DQ7             | 43.4               | -150.3 | 1102      | -3817 |  |

| 024 | CE#             | 51.5               | -147.3 | 1308      | -3741 |  |

| 025 | A10             | 61.6               | -145.8 | 1565      | -3703 |  |

| 026 | OE#             | 69.5               | -142.1 | 1766      | -3610 |  |

| 027 | A11             | 69.9               | 141.9  | 1775      | 3604  |  |

| 028 | A9              | 61.6               | 146.9  | 1565      | 3730  |  |

| 029 | A8              | 52.1               | 150.3  | 1322      | 3817  |  |

| 030 | A13             | 38.7               | 150.3  | 983       | 3817  |  |

# 1.1 Pad Description

Table 1. 28F020 2048K (256K x 8) Flash Memory Bond Pad Center Data

|     | Signal          | Pad Center         |       |           |      |

|-----|-----------------|--------------------|-------|-----------|------|

| Pad |                 | (Mils = 0.001 in.) |       | (Microns) |      |

|     |                 | Х                  | Υ     | Х         | Υ    |

| 031 | A14             | 27.4               | 150.3 | 695       | 3817 |

| 032 | A17             | 19.3               | 150.3 | 490       | 3817 |

| 033 | WE#             | 11.9               | 150.3 | 303       | 3817 |

| 034 | V <sub>CC</sub> | 4.6                | 147.0 | 117       | 3735 |

- Notes:

1. The symbol "#" is used at the end of the signal name to denote an active low signal.

2. X-Y pad coordinates represent bond pad centers and are relative to center of die.

PRELIMINARY 5

# 2.0 INTEL DIE PRODUCTS PROCESSING

#### **TEST PROCEDURE**

Intel has instituted full-speed functional testing at the die level for all SmartDie products. This level of testing is ordinarily performed only after assembly into a package. Each die is tested to the same electrical limits as the equivalent packaged unit.

### **WAFER PROBE**

Wafer probing is performed on every wafer produced in an Intel Fab. The process consists of specific electrical tests and device-specific functionality tests

At the wafer level, built-in test structures are probed to verify that device electrical characteristics are in control and meet specifications. Measurements are made of transistor threshold voltages and current characteristics; poly and contact resistance; gate oxide and junction integrity; and specific parameters critical to the particular technology and device type. Wafer-to-wafer, across-the-wafer run-to-run variation and conformance to spec limits are checked.

The actual devices on each wafer are then probed for both functionality and performance to specifications. Additional reliability tests are also included in the probe steps.

#### **WAFER SAW**

Probed wafers are transferred to Intel's assembly sites to be sawed. The saw cuts completely through the wafer.

#### **DIE INSPECTION**

Upon completion of the wafer saw, the die are moved to pick and place equipment that removes reject die. The remaining die are submitted to the same visual inspection as our standard packaged product. The compliant die are then transferred to GEL-PAKs for shipment.

#### **PACKING PROCEDURE**

Intel will ship all Intel die products in GEL-PAKs. GEL-PAKs eliminate the die edge damage usually associated with die cavity plates or chip trays.

The backside of each die adheres to the gel membrane in the GEL-PAK, eliminating the risk of damage to the active die surface. A simple vacuum release mechanism allows for pick and place removal at the customer's site.

Only die from the same wafer lot are packaged together in a GEL-PAK, and all die are placed in the GEL-PAKs with a consistent orientation. The GEL-PAKs are then sealed and labeled with the following information:

- Intel Die Products

- Intel Part Number

- Spec

- Customer Part Number (if applicable)

- Fab Lot Number

- Quantity

- · Assembly Lot Traveler Number

- Seal Date

- ROM Code (if applicable)

#### NOTE:

GEL-PAKs require a Vacuum Release Station. Contact Vichem Corporation for more information.

#### **INSPECTION STEPS**

Multiple inspection steps are performed during the die fabrication and packing flow. These steps are performed according to the same specifications and criteria established for Intel's standard packaged product. Specific inspection steps include a wafer saw visual as well as a final die visual just before die are sealed in moisture barrier bags.

#### STORAGE REQUIREMENTS

Intel die products will be shipped in GEL-PAKs and sealed in a moisture-barrier anti-static bag with a desiccant. No special storage procedures are required while the bag is still unopened. Once opened, the GEL-PAK should be stored in a dry, inert atmosphere to prevent bond pad corrosion.

#### **ESD**

Components are ESD sensitive.

# intel®

### 28F020 28F020 2048K (256K x 8) FLASH MEMORY

#### 3.0 SPECIFICATIONS

Specifications within this document are specific to a particular die revision and are subject to change without notice. Verify with your local Intel Sales Office that you have the latest data before finalizing a design.

# 3.1 28F020 2048K (256K x 8) Flash Memory Handling Requirements

There are two key areas of concern for the 28F020 Flash Memory product. The first is our recommendation to avoid exposing Flash devices to ultraviolet light. Erasing the device under a UV light erases not only the bits in the array but also the device-specific control information stored in the chips. The second area of concern is in the exposure of the 28F020 Flash Memory product to temperatures above 475°C for more than 10 minutes. Exposure above this time/temperature envelope may cause damage to the device reference cells.

# 3.2 28F020 2048K (256K x 8) Flash Memory Physical Specifications

Substrate Bias Condition: Self-biasing to  $V_{SS}$ . Alternative is to drive  $V_{SS}$ .

### 3.3 DC Specifications

#### **ABSOLUTE MAXIMUM RATINGS\***

#### **OPERATING CONDITIONS\***

| Digital Supply Voltage ( $V_{CC}$ ). | 4.5V to 5.5V                      |

|--------------------------------------|-----------------------------------|

| Junction Temperature under I         | Bias (T <sub>J</sub> )0°C to 80°C |

Post-saw die dimensions:

Mils:  $X = 155 \pm 0.5$ ,  $Y = 316 \pm 0.5$ See associated Die/Bond Pad Layout for X,Y orien-

tation.

Die Backside: Polished bare silicon.

Pad Passivation Opening Size:

Mils: 4.1 x 4.1 Microns: 105.0 x 105.0 Die Thickness: 17  $\pm$  1 mils

Pad Pitch:

Pads are not all evenly pitched. Minimum pitch is 185 microns (7.3 mils).

Bond Pad Metalization (outermost layer listed first)

0.9 microns Aluminum (0.5% copper)

0.1 micron Titanium

Die Revision: B

Pads per Die: 34

Intel Fabrication Process: ETOX™ III (minimum feature size 0.8 micron).

Passivation: (from top surface)

2.3 microns B-Pyrox

1.1 microns Oxynitride

**NOTICE:** This document contains preliminary information on new products in production. It is valid for the devices indicated in the revision history. This specification is subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

PRELIMINARY 7

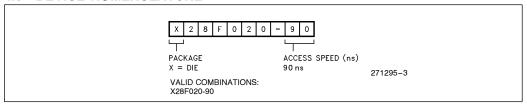

# 4.0 DEVICE NOMENCLATURE

# 5.0 REFERENCE INFORMATION

| Title                                                                       |        |  |

|-----------------------------------------------------------------------------|--------|--|

| 28F020 2-Mbit Flash Memory                                                  | 290245 |  |

| ER-20, ETOX™ II Flash Memory Technology                                     | 294005 |  |

| ER-24, Intel Flash Memory                                                   | 294008 |  |

| RR-60, ETOX™ II Flash Memory Reliability Data Summary                       | 293002 |  |

| AP-316, Using Flash Memory for In-System Reprogrammable Nonvolatile Storage | 292046 |  |

| AP-325, Guide to Flash Memory Reprogramming                                 |        |  |

# 6.0 REVISION HISTORY

| Rev | Date | Description                                                                              |  |

|-----|------|------------------------------------------------------------------------------------------|--|

| 001 | 3/94 | Original version.                                                                        |  |

| 002 | 6/94 | Replace Figure 1 to add GEL-PAK orientation information. General rewrite of Section 2.0. |  |