- Optimum Integration for Lowest Cost Solution

- IEEE 802.3 10Base-T and 100Base-T compatible

- Glueless 32-bit PCI bus master interface

- Flash support up to 1 Mbyte

- High Performance Networking Functions

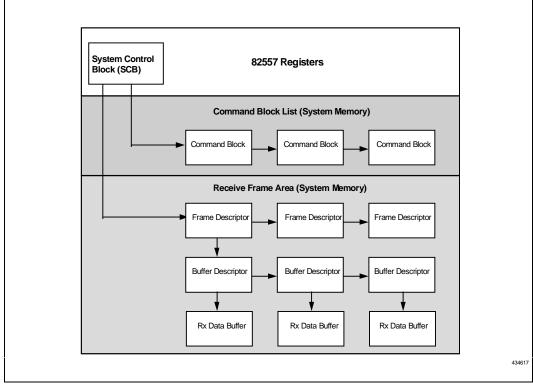

- Chained memory structure similar to the 82596 controller

- Improved dynamic transmit chaining

- Programmable transmit threshold

- Early receive interrupt

- Large, 3 Kbyte internal receive and transmit FIFOs

- Back to back transmit at 100 Mbps, within minimum IFS

- Ease of Use

- Built-in interface to MII compliant physical layer devices

- Standard seven pin ENDEC interface to serial device such as the Intel 82503 for 10 Mbps only designs

- Full or half duplex capable at 10 or 100 Mbps

- EEPROM support

- Internal counters for network management

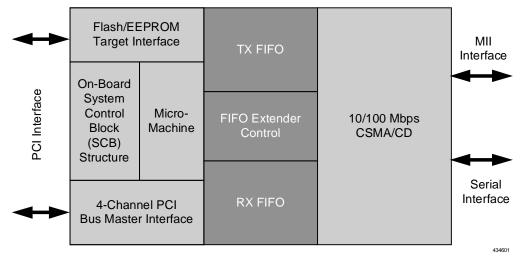

# Parallel Side

# Serial Side

Intel 82557 Block Diagram

October 1996 Order Number: 644346-003

#### This complete document is available from Intel's World Wide Website and/or U.S. Literature Center:

World Wide Website: http://www.intel.com

U.S. Literature Center: 800-548-4725

in other geographies, please contact your local sales office.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

\*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683 COPYRIGHT © INTEL CORPORATION, 1996

# **CONTENTS**

| PAGE                                            | PAGE                                      |

|-------------------------------------------------|-------------------------------------------|

| 1.0. INTRODUCTION5                              | 4.3.1.1. 10/100 Mbps MII Transmission34   |

| 1.1. 82557 Overview5                            | 4.3.1.2. 10/100 Mbps MII Reception34      |

| 1.2. Features and Enhancements5                 | 4.3.2. 10/100 MII MBPS FULL DUPLEX        |

| 1.3. Compliance to Industry Standards5          | OPERATION34                               |

| 1.3.1. Other Literature6                        | 4.3.3. 10 MBPS-ONLY INTERFACE35           |

| 1.3.1. Other Literature                         | 4.3.3.1. 10 Mbps Transmission35           |

| 2.0. PIN DEFINITIONS6                           | 4.3.3.2. 10 Mbps Reception35              |

| 2.1. PCI Bus Interface Signals6                 | 4.3.3.3. 10 Mbps Full Duplex Operation35  |

| 2.1.1. SIGNAL TYPE DEFINITION8                  | 4.4. MII Management Interface35           |

| 2.1.2. ADDRESS AND DATA PINS8                   | 4.4.1. MDI CYCLES35                       |

| 2.1.3. INTERFACE CONTROL PINS9                  | 5.0. 82557 SOFTWARE INTERFACE36           |

| 2.1.4. ERROR REPORTING PINS10                   | 5.1. The Shared Memory Communication      |

| 2.1.5. INTERRUPT PIN10                          | Architecture36                            |

| 2.1.6. ARBITRATION PINS10                       | 5.2. Initializing the 8255738             |

| 2.1.7. SYSTEM PINS10                            | 5.3. Controlling the 8255738              |

| 2.2. Local Memory Interface11                   | 5.3.1. THE 82557 CONTROL/STATUS           |

| 2.3. Serial Interface Pins12                    | REGISTER (CSR)38                          |

| 2.4. Power and Ground13                         | 5.3.1.1. Statistical Counters39           |

| 2.5. Test Access Port (TAP)14                   | 6.0. ELECTRICAL SPECIFICATIONS AND        |

| 3.0. 82557 ARCHITECTURE OVERVIEW14              | TIMINGS42                                 |

| 3.1. Parallel Subsystem Overview14              | 6.1. Absolute Maximum Ratings42           |

| 3.2. FIFO Subsystem Overview15                  | 6.2. DC Specifications42                  |

| 3.3. 10/100 Mbps Serial CSMA/CD Unit            | 6.3. AC Specifications44                  |

| Overview15                                      | 6.3.1. PCI INTERFACE44                    |

| 4.0 THE COSES HARRINGS INTERES OF               | 6.4. Timing Specification45               |

| 4.0. THE 82557 HARDWARE INTERFACE16             | 6.4.1. CLOCK SPECIFICATIONS45             |

| 4.1. PCI Bus Interface                          | 6.4.1.1. PCI Interface Clock45            |

| 4.1.1. PCI CONFIGURATION16                      | 6.4.1.2. MII Interface Clock45            |

| 4.1.1.1. PCI Configuration Space Organization16 | 6.4.1.3. 10 Mbps Serial Interface Clock45 |

| 4.1.1.2. PCI Configuration Registers17          | 6.4.2. TIMING PARAMETERS46                |

| 4.1.2. 82557 BUS OPERATIONS                     | 6.4.2.1. PCI Timings46                    |

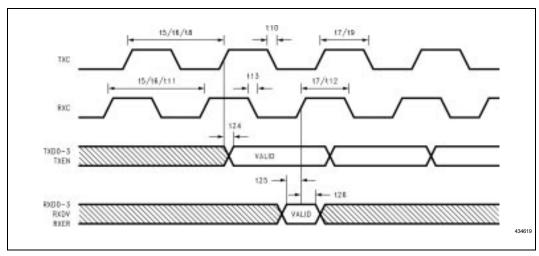

| 4.1.2.1. General Overview                       | 6.4.2.2. MII and 10 Mbps Interface        |

| 4.2. FLASH/EEPROM Interface31                   | Timings47                                 |

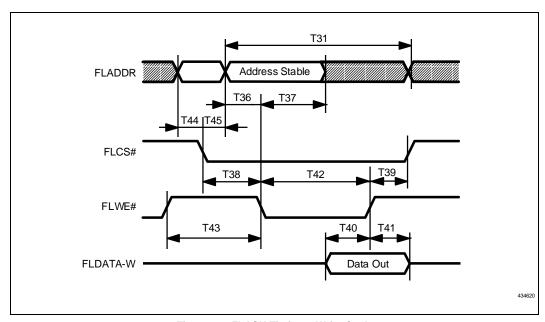

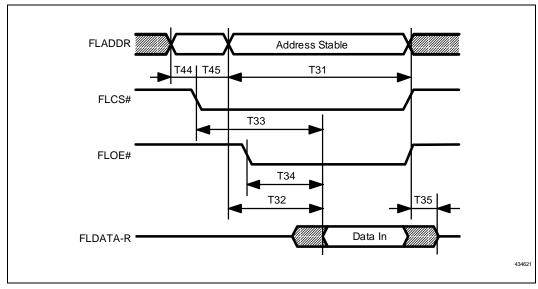

| 4.2.1. FLASH INTERFACE OPERATION31              | 6.4.2.3. Collision Parameters48           |

| 4.2.2. SERIAL EEPROM INTERFACE33                | 6.4.2.4. FLASH Interface Timings49        |

| 4.2.2. SERIAL EEPROW INTERFACE                  | 7.0. PHYSICAL ATTRIBUTES AND              |

| 4.3.1. 10/100 MBPS MII COMPATIBLE               | DIMENSIONS50                              |

| INTERFACE34                                     | 8.0. REVISION HISTORY52                   |

**FIGURES**

| Table 1. PCI Configuration Registers                      | 17 |

|-----------------------------------------------------------|----|

| Table 2. Device Identification Registers                  | 18 |

| Table 3. PCI Command Register Bits                        | 19 |

| Table 4. PCI Status Register Bits                         | 21 |

| Table 5. Miscellaneous PCI Configuration Bits.            | 22 |

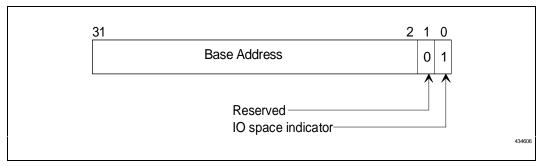

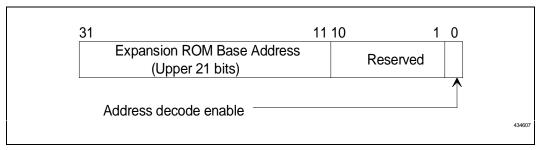

| Table 6. 82557 Base Address Registers                     | 24 |

| Table 7. 82557 Expansion ROM Base Address Register Format |    |

| Table 8. Summary of Reset Commands                        |    |

| Table 9. Control/Status Register                          | 39 |

| Table 10. Statistical Counters                            | 40 |

| Table 11. General DC Specifications                       | 42 |

| Table 12. PCI Interface DC Specifications                 | 42 |

| Table 13. MII and 10 Mbps PHY Interface DC Specifications | 43 |

| Table 14. FLASH/EEPROM Interface DC Specifications        | 43 |

| Table 15. AC Specifications for PCI Signaling             |    |

| Table 16. PCI Clock Specifications                        | 45 |

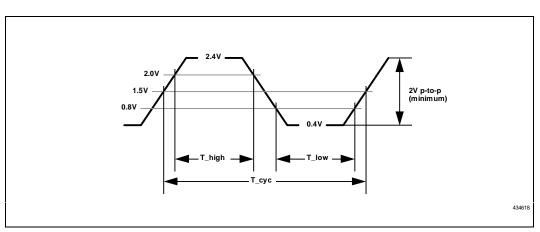

| Table 17. MII Clock Specifications                        | 45 |

| Table 18. Serial Interface Clock Specifications.          | 46 |

| Table 19. PCI Timing Parameters                           | 46 |

| Table 20. MII and Serial Interface Timing Parameters      | 47 |

| Table 21. FLASH Interface Timing Parameters               | 48 |

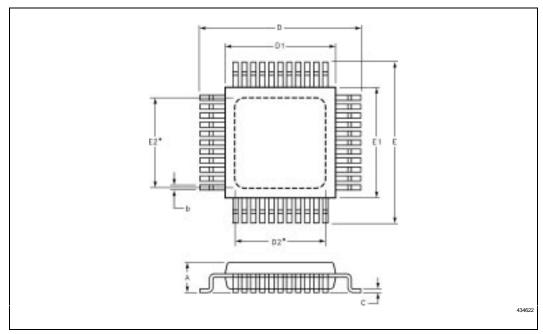

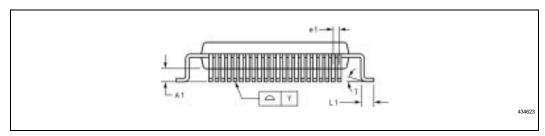

| Table 22. Intel 82557 Package Attributes                  |    |

| Table 23 Quad Flatnack Dimensions*                        | 52 |

**TABLES**

## 1.0. INTRODUCTION

# 1.1. 82557 Overview

The 82557 is Intel's first highly integrated 32-bit PCI LAN controller for 10 or 100 Mbps Fast Ethernet networks. The 82557 offers a high performance LAN solution while maintaining low-cost through its high-integration. It contains a 32-bit PCI Bus Master interface to fully utilize the high bandwidth available (up to 132 Mbytes per second) to masters on the PCI bus. The bus master interface can eliminate the intermediate copy step in Receive (RCV) and Transmit (XMT) frame copies, resulting in faster processing of these frames. It maintains a similar memory structure to the Intel 82596 LAN Coprocessor, however, these memory structures have been streamlined for better network operating (NOS) interaction improved system and performance.

The 82557 contains two large receive and transmit FIFOs (3 Kbytes each) which prevent data overruns or underruns while waiting for access to the PCI bus, as well as enabling back to back frame transmission within the minimum 960 nanosecond inter frame spacing. Full support for up to 1 Mbyte of FLASH enables network management support via Intel FlashWorks utilities as well as remote boot capability (a BIOS extension stored in the FLASH which could allow a node to boot itself off of a network drive). For 100 Mbps applications, the 82557 contains an IEEE MII compliant interface to the Intel 82553 serial interface device (or other MII compliant PHYs) which will allow connection to 100/10 Mbps networks. For 10 Mbps networks, the 82557 can be interfaced to a standard ENDEC device (such as the Intel 82503 Serial Interface), while maintaining software compatibility with 100 Mbps solutions.

The 82557 is designed to implement cost effective, high performance PCI add-in adapters, PC motherboards, or other interconnect devices such as hubs or bridges. Its combination of high integration and low cost make it ideal for these applications.

## 1.2. Features and Enhancements

The following list summarizes the main features of the Intel 82557 controller:

- Glueless 32-bit PCI Bus Master Interface (Direct Drive of Bus), compatible with PCI Bus Specification, revision 2.1

- 82596-like Chained Memory Structure

- Improved dynamic transmit chaining for enhanced performance

- Programmable transmit threshold for improved bus utilization

- Early receive interrupt for concurrent processing of receive data

- FLASH support up to 1Mbyte

- Large on-chip receive and transmit FIFOs (3 Kbytes each)

- · On-chip counters for network management

- Back to back transmit at 100 Mbps

- EEPROM support

- Support for both 10 Mbps and 100 Mbps Networks

- Interface to MII compliant PHY devices, including Intel 82553 Physical Interface component for 10/100 Mbps designs

- IEEE 802.3u 100Base-T, TX, and T4 compatible

- Interface to Intel 82503 or other serial device for 10 Mbps designs: IEEE 802.3 10Base-T compatible

- Autodetect and autoswitching for 10 or 100 Mbps network speeds

- Full or half duplex-capable at 10 and 100 Mbps

- 160-Lead QFP package

# 1.3. Compliance to Industry Standards

The 82557 has two interfaces. The host system PCI bus interface and the serial or network interface. The network interface complies to the IEEE standard for 10BASET-T, TX, and T4 and 100Base-T, TX, and T4 Ethernet interfaces. The 82557 also complies to the PCI Bus Specification. Revision 2.1.

#### 1.3.1. Other Literature

This data sheet provides complete pin identification, definitions and electrical specifications. It also provides an overview of each main subsystem within the component. Most of this information is aimed at hardware design engineers.

Software engineers and others who are designing interfaces or writing device drivers for this component, should refer to the *82557 User's Manual*. This document provides more detailed information on feature sets, register descriptions and implementation steps for various functions.

## 2.0. PIN DEFINITIONS

Figure 1 shows pin numbering and signal identification for the 82557. Sections 2.1 through 2.5 describe the signals.

# 2.1. PCI Bus Interface Signals

The following sections describe the 82557 pins and signals by function.

Figure 1. Device Pinout, Top View

# 2.1.1. SIGNAL TYPE DEFINITION

| IN  | Input is a standard input-only signal                                                                                                                                                          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT | Totem Pole Output is a standard active driver.                                                                                                                                                 |

| TS  | Tri-State is a bi-directional, tri-state input/output pin.                                                                                                                                     |

| STS | Sustained Tri-State is an active low tri-state signal owned and driven by the 82557. When the 82557 drives this pin low, it must drive it high for at least one clock before letting it float. |

| OD  | Open Drain allows multiple devices to share as a wired-OR.                                                                                                                                     |

# 2.1.2. ADDRESS AND DATA PINS

| Symbol | Pin | Туре | Name and Function                                                           |

|--------|-----|------|-----------------------------------------------------------------------------|

| AD0    | 94  | TS   | Address and Data are multiplexed on the same PCI pins by the 82557. A bus   |

| AD1    | 93  |      | transaction consists of an address phase followed by one or more data       |

| AD2    | 90  |      | phases. The address phase is the clock cycle in which FRAME# is asserted.   |

| AD3    | 89  |      | During the address phase AD0-31 contain a physical address (32 bits). For   |

| AD4    | 86  |      | I/O, this is a byte address; for configuration and memory, a DWORD address. |

| AD5    | 85  |      | The 82557 uses 'Little Endian' byte ordering. During data phases AD0-7      |

| AD6    | 82  |      | contain the least significant byte (LSB) and AD24-31 contain the most       |

| AD7    | 81  |      | significant byte (MSB).                                                     |

| AD8    | 77  |      |                                                                             |

| AD9    | 74  |      |                                                                             |

| AD10   | 73  |      |                                                                             |

| AD11   | 72  |      |                                                                             |

| AD12   | 71  |      |                                                                             |

| AD13   | 68  |      |                                                                             |

| AD14   | 67  |      |                                                                             |

| AD15   | 66  |      |                                                                             |

| AD16   | 49  |      |                                                                             |

| AD17   | 48  |      |                                                                             |

| AD18   | 47  |      |                                                                             |

| AD19   | 44  |      |                                                                             |

| AD20   | 43  |      |                                                                             |

| AD21   | 40  |      |                                                                             |

| AD22   | 39  |      |                                                                             |

| AD23   | 36  |      |                                                                             |

| AD24   | 31  |      |                                                                             |

| AD25   | 30  |      |                                                                             |

| AD26   | 27  |      |                                                                             |

| AD27   | 26  |      |                                                                             |

| AD28   | 24  |      |                                                                             |

| AD29   | 23  |      |                                                                             |

| AD30   | 20  |      |                                                                             |

| AD31   | 19  |      |                                                                             |

| Symbol                           | Pin                  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBE#0<br>CBE#1<br>CBE#2<br>CBE#3 | 78<br>65<br>50<br>35 | TS   | Bus Command and Byte Enables are multiplexed on the same PCI pins by the 82557. During the address phase of a transaction, C/BE0-3# define the bus command. During the data phase C/BE0-3# are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data. C/BE0# applies to byte 0 (LSB) and C/BE3# applies to byte 3 (MSB).                                                                                                     |

| PAR                              | 62                   | TS   | Parity is even parity across AD0-31 and C/BE0-3#. PAR is stable and valid one clock after the address phase. For data phases, PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted on a read transaction. Once PAR is valid, it remains valid until one clock after the completion of the current data phase. When the 82557 is a bus master, it drives PAR for address and write data phases. As a slave, it drives PAR for read data phases. |

# 2.1.3. INTERFACE CONTROL PINS

| Symbol | Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAME# | 53  | STS  | Frame# is driven by the 82557 to indicate the beginning and duration of an access. FRAME# is asserted to indicate a bus transaction is beginning. While FRAME# is asserted, data transfers continue. When FRAME# is deasserted, the transaction is in the final data phase.                                                                                                                                                                                                                                                                                                           |

| IRDY#  | 54  | STS  | Initiator Ready# indicates the ability of the 82557 (as a bus mastering device) to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#. A data phase is completed on any clock in which both IRDY# and TRDY# are sampled asserted. During a write, IRDY# indicates that valid data is present on AD0-31. During a read, it indicates the master is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY# are asserted together. The 82557 drives IRDY# when acting as a master, and samples it when acting as a slave. |

| TRDY#  | 55  | STS  | Target Ready# indicates the ability of the 82557 (as a selected device) to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#. A data phase is completed on any clock in which both TRDY# and IRDY# are sampled asserted. During a read, TRDY# indicates that valid data is present on AD0-31. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted until both TRDY# and IRDY# are asserted together. The 82557 drives TRDY# when acting as a slave, and samples it when acting as a master.         |

| STOP#  | 59  | STS  | Stop# indicates the current target is requesting the master to stop the current transaction. As a slave, the 82557 drives STOP# to inform the bus master to stop the current transaction. As a bus master, the 82557 receives STOP# from the slave and stops the current transaction.                                                                                                                                                                                                                                                                                                 |

| IDSEL  | 34  | IN   | Initialization Device Select is used by the 82557 as a chip select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Symbol  | Pin | Туре | Name and Function                                                                                                                                                                                                                              |

|---------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVSEL# | 56  | STS  | Device Select#, when actively driven by the 82557 as a slave, indicates to the bus master that it has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected. |

# 2.1.4. ERROR REPORTING PINS

| Symbol | Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERR#  | 60  | OD   | System Error# is used by the 82557 to report address parity errors. SERR# is open drain and is actively driven for a single PCI clock when reporting the error.                                                                                                                                                                                                                                   |

| PERR#  | 61  | STS  | Parity Error# is used by the 82557 for reporting data parity errors during all PCI transactions except a Special Cycle. The PERR# pin is sustained tri-state and must be driven active by the 82557 after receiving data two clocks following the data when a data parity error is detected. The minimum duration of PERR# is one clock for each data phase that a data parity error is detected. |

## 2.1.5. INTERRUPT PIN

| Symbol | Pin | Туре | Name and Function                                                                                                   |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------|

| INTA#  | 18  | OD   | Interrupt A# is used to request an interrupt by the 82557. This is an active low, level-triggered interrupt signal. |

## 2.1.6. ARBITRATION PINS

| Symbol | Pin | Туре | Name and Function                                                                                                                        |

|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------|

| REQ#   | 15  | TS   | Request# indicates to the arbiter that the 82557 desires use of the bus. This is a point-to-point signal. Every master has its own REQ#. |

| GNT#   | 14  | IN   | Grant# indicates to the 82557 that access to the bus has been granted. This is a point to point signal.                                  |

# 2.1.7. SYSTEM PINS

| Symbol | Pin | Туре | Name and Function                                                                                                                                                                                                                                          |

|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK    | 25  | IN   | Clock provides timing for all transactions on the PCI bus and is an input to the 82557. All other PCI signals, except RST# and the INT# lines are sampled on the rising edge of CLK and all other timing parameters are defined with respect to this edge. |

| Symbol | Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST#   | 13  | IN   | Reset# is used to bring PCI-specific registers, sequencers and signals to a consistent state. Anytime RST# is asserted, all PCI output signals must be driven to their benign state. In general, this means they must be tri-stated. SERR# (open drain) is floated. To prevent AD, C/BE# and PAR signals from floating during reset, the central device may drive these lines during reset (bus parking) only to a logic low level; they may not be driven high. |

# 2.2. Local Memory Interface

| Symbol                                                                                                                             | Pin                                                                              | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EECS                                                                                                                               | 138                                                                              | OUT  | EEPROM Chip Select. Used to assert chip select to the serial EEPROM. EECS is active-high.                                                                                                                                                                                                                                                                                                                  |  |

| FLD0EESK                                                                                                                           | 135                                                                              | TS   | Multiplexed pin. During flash access, this pin acts as FLASH Data 0 input/output. During EEPROM access it acts as EEPROM SHIFT CLOCK output to shift data into and out of the serial EEPROM.                                                                                                                                                                                                               |  |

| FLD1EEDO                                                                                                                           | 134                                                                              | TS   | Multiplexed pin. During flash access, this pin acts as FLASH Data 1 input/output. During EEPROM access, this pin acts as the input EEPROM DATA OUT.                                                                                                                                                                                                                                                        |  |

| FLD2EEDI                                                                                                                           | 133                                                                              | TS   | Multiplexed pin. During flash access, this pin acts as FLASH Data 2 input/output. During EEPROM access, this pin acts as the output EEPROM DATA IN.                                                                                                                                                                                                                                                        |  |

| FLD3<br>FLD4<br>FLD5<br>FLD6<br>FLD7                                                                                               | 130<br>129<br>128<br>127<br>124                                                  | TS   | FLASH Data 7 to 3 input/outputs.                                                                                                                                                                                                                                                                                                                                                                           |  |

| FLADDR0<br>FLADDR1<br>FLADDR2<br>FLADDR3<br>FLADDR4<br>FLADDR5<br>FLADDR6<br>FLADDR7<br>FLADDR8<br>FLADDR9<br>FLADDR10<br>FLADDR11 | 123<br>120<br>119<br>118<br>115<br>114<br>109<br>108<br>107<br>104<br>103<br>102 | OUT  | FLASH Address 11 to 0 work in conjunction with an external 8-bit Address Latch to control the FLASH addressing up to 1Mbyte. The 8 most significant FLASH address pins (FLADDR11 to 4) should be connected to both the Address Latch and to Address Pins 11 to 4 of the FLASH. The Address Latch provides the upper 8-bits, 19 to 12, of address to the FLASH and is loaded by assertion of the FLCS# pin. |  |

| Symbol | Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                   |  |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FLCS#  | 96  | OUT  | FLASH Chip Select will normally be high to disable access to the FLASH. Whenever a FLASH high address is to be latched, FLCS# will go low, thus latching the data in the latch and enabling the FLASH. FLCS# should be connected to both the ENABLE pin on the external address latch and the CE# pin on the FLASH. |  |

| FLOE#  | 98  | OUT  | FLASH Output Enable provides the active low Output Enable control to the FLASH.                                                                                                                                                                                                                                     |  |

| FLWE#  | 101 | OUT  | FLASH Write Enable provides the active low Write Enable control to the FLASH.                                                                                                                                                                                                                                       |  |

# 2.3. Serial Interface Pins

| Symbol                       | Pin                      | Туре | Name and Function                                                                                                                                                                                              |  |

|------------------------------|--------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RXCLK                        | 151                      | IN   | Receive Clock operates at either 25 MHz, 2.5 MHz (MII Mode), or 10 MHz (10 Mbps-only mode).                                                                                                                    |  |

| RXD0<br>RXD1<br>RXD2<br>RXD3 | 150<br>149<br>148<br>147 | IN   | Receive Data 0 - 3: nibble-wide data inputs in MII mode. In 10 Mbps only mode, RXD0 is the serial receive data input.                                                                                          |  |

| RXDV                         | 153                      | IN   | Receive Data Valid indicates that valid data is present on the RXD lines. This is used for MII mode only. When this pin is inactive (low), receive data is not sampled by the 82557.                           |  |

| RXER                         | 152                      | IN   | Receive Data Error indicates that an invalid symbol has been detected inside a receive packet. This is used in MII mode only.                                                                                  |  |

| RXCONG                       | 1                        | OUT  | Receive Congestion is used in duplex mode and is asserted when the receive FIFO is full and unable to accept any more data packets. Please refer to the National Semiconductor Corporation PHY implementation. |  |

| CRS                          | 155                      | IN   | Carrier Sense indicates traffic on the wire.                                                                                                                                                                   |  |

| TXCLK                        | 8                        | IN   | Transmit Clock operates at either 25 MHz, 2.5 MHz (MII Mode), or 10 MHz (10 Mbps only mode).                                                                                                                   |  |

| TXD0<br>TXD1<br>TXD2<br>TXD3 | 7<br>6<br>3<br>2         | OUT  | Transmit Data 0 - 3 nibble wide transmit data outputs in MII mode. In 10 Mbp only mode TXD0 is the serial transmit data output.                                                                                |  |

| RTS/TXEN                     | 158                      | OUT  | Request To Send indicates that the 82557 has a frame pending for transmission (10 Mbps-only mode)  Transmit Enable indicates that the 82557 is transferring data to the PHY (MII mode).                        |  |

| COL                          | 154                      | IN   | Collision Detect indicates a collision has been detected on the wire. In Full Duplex mode, assertion of COL indicates a Congestion condition has occurred.                                                     |  |

| Symbol | Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TXRDY  | 144 | IN   | Transmit Ready is used in duplex mode for flow control. Please refer to the National Semiconductor Corporation PHY implementation.                                                                                                                                                                                                                                                                    |  |

| RSTOUT | 146 | OUT  | Reset Out signal to the PHY is driven high during H/W reset of the 82557.                                                                                                                                                                                                                                                                                                                             |  |

| LPBCK  | 145 | OUT  | Loopback controls the PHY into loopback mode.                                                                                                                                                                                                                                                                                                                                                         |  |

| FDX#   | 143 | IN   | Full Duplex is an input from the physical layer component indicating if it has switched into or out of full duplex mode. FDX# is active low.                                                                                                                                                                                                                                                          |  |

| FULHAL | 6   | OUT  | Full/Half Duplex. When active, indicates 82557 is in full duplex mode. This pin is multiplexed with the TXD1 pin and operates only when in 10 Mbps-only mode.                                                                                                                                                                                                                                         |  |

| MDIO   | 156 | TS   | Management Data Input/Output is a bi-directional signal between the 82557 and an MII-compatible PHY. It is used to transfer control and status information between the 82557 and the PHY. Control information is driven by the 82557 on the MDIO synchronously to MDC and sampled synchronously by the PHY. Status information is driven synchronously by the PHY and sampled synchronously by 82557. |  |

| MDC    | 157 | OUT  | Management Data Clock provides timing reference for transfer of control information and status on the MDIO signal. The frequency of this clock is up to 2.5 MHz.                                                                                                                                                                                                                                      |  |

# 2.4. Power and Ground

| Symbol          | Pin                                                                                                                            | Туре | Name and Function |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------|------|-------------------|

| Vcc             | 4, 9, 12, 16, 21, 28, 32, 37, 42, 45, 51, 57, 63, 69, 75, 79, 83, 88, 92, 97, 100, 106, 110, 113, 117,122, 126, 132, 137, 159  | In   | Power: +5V ± 5%.  |

| V <sub>SS</sub> | 5, 10, 11, 17, 22, 29, 33, 38, 41, 46, 52, 58, 64, 70, 76, 80, 84, 87, 91, 95, 99, 105, 111, 112, 116, 121, 125, 131, 136, 160 | In   | Ground: 0V.       |

# 2.5. Test Access Port (TAP)

The 82557 Test Access Port consists of four pins: TI, TOUT, TCK, and TEXEC. The following table

summarizes the signal descriptions for these pins. For more information about the TAP, refer to Application Note 375.

| Symbol | Pin | Туре | Name and Function                                                                                                                                                             |  |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TI     | 142 | 1    | Test Input port is a serial input of test command data.                                                                                                                       |  |

| TOUT   | 141 | 0    | Fest Output port is a serial output of test com-mand data. TOUT is determined according to the last test command executed.                                                    |  |

| тск    | 140 | I    | Test Input Clock. The clock of the test access port logic. TI data is sampled nto the test command logic.                                                                     |  |

| TEXEC  | 139 | I    | Load Instruction Test Register. Issues the new test command when asserted. The command is loaded serially via the TI input and then sampled to the Instruction Test Register. |  |

# 3.0. 82557 ARCHITECTURE OVERVIEW

The figure on the cover shows a high level block diagram of the 82557 part. It is divided into three main subsystems: a parallel subsystem, a FIFO subsystem and the 10/100 Mbps CSMA/CD unit.

# 3.1. Parallel Subsystem Overview

The parallel subsystem is broken down into several functional blocks: a PCI Bus Master Interface, a Micro Machine processing unit and its corresponding microcode ROM, and a PCI Target Control/FLASH/EEPROM interface. The parallel subsystem also interfaces to the FIFO subsystem, passing data (XMT, RCV and Configuration), command and status parameters between these two blocks.

The PCI Bus Master Interface provides a complete interface to a PCI bus and is compliant with revision 2.1 of the PCI Bus Specification. No external logic is required to interface the 82557 to a PCI bus. The 82557 provides 32 bits of addressing and data, as well as the complete control interface to operate on a PCI bus. As a PCI target, it follows the PCI Configuration format which allows all accesses to the 82557 (control register, FLASH accesses, boot, etc.) to be automatically mapped into free memory and I/O space upon initialization of a PCI system. For processing of XMT and RCV frames, the 82557 operates as a master on the PCI bus, initiating zero wait state transfers for accessing these data parameters.

The PCI Bus Master Interface consists of three units. The Bus Interface Unit (BIU) controls the access to the PCI bus according to the bus protocol. The BIU controls such actions as initiating when to request or relinquish the external PCI bus and handles internal direct memory access (DMA) channel arbitration. The Data Interface Unit (DIU) routes data into and out of the 82557 at high speed data transfers. The DMA unit controls the addressing for four separate DMA channels.

The 82557 Control/Status Register Block is contained as part of the PCI target element. The Control/Status Register Block consists of the following 82557 internal control registers: System Control Block (SCB), PORT, FLASH control register, EEPROM control register and Management Data Interface (MDI) Control register. Refer to the 82557 User's Manual for more information on the Control/Status Register Block.

The Micro Machine is an embedded processing unit contained in the 82557. The Micro Machine accesses the 82557 microcode ROM working its way through the op-codes (or instructions) contained in the ROM to perform its functions. Parameters accessed from memory such as Transmit Buffer Descriptor fields or pointers to data buffers are also used by the micro machine during processing of RCV or XMT frames by the 82557. A typical function of the Micro Machine would be to take a data buffer pointer field and load it into the 82557 DMA unit for direct access to the data buffer. The Micro Machine is divided into two units, a Receive Unit and a Command Unit (including XMT functions). These two units operate independently and concurrently. Control is switched between the two units according to the microcode instruction flow.

The independence of the Receive and Command units of the Micro Machine allows the 82557 to execute commands and receive incoming frames simultaneously, with no real-time CPU intervention.

The 82557 contains an interface to both an external FLASH memory and an external serial EEPROM. The FLASH interface, which could also be used to connect to any standard 8-bit EPROM device, provides up to 1 Mbyte of addressing to the FLASH. It utilizes a multiplexed address scheme that works in conjunction with an LS373 or compatible latch to demultiplex the address. Without the latch, up to 16 Kbytes can be addressed. Both Read and Write accesses are supported. The FLASH may be used for remote boot functions, network statistical and diagnostics functions, etc. The FLASH is mapped into host system memory (anywhere within the 32-bit memory address space) for software accesses. It is also mapped into an available boot expansion ROM location during boot time of the system. For more information on the FLASH interface, see Section 4.1.3. The EEPROM is used to store relevant information for a LAN connection such as Node Individual Address, as well as board manufacturing and configuration information. Both Read and Write accesses to the EEPROM are supported by the 82557. For more information on the EEPROM interface, see Section 4.1.3.

# 3.2. FIFO Subsystem Overview

The 82557 FIFO subsystem consists of a 3 Kbyte transmit FIFO and 3 Kbyte receive FIFO. Each FIFO is unidirectional and independent of the other. The FIFO subsystem serves as the interface between the 82557 parallel side and the serial CSMA/CD unit. It provides a temporary buffer storage area for frames as they are either being received or transmitted by the 82557. This allows for several important features in the 82557:

- Transmit frames can be queued within the XMT FIFO, allowing back to back transmission within the minimum Inter Frame Spacing (IFS)

- The storage area in the FIFO area allows the 82557 to withstand long PCI Bus latencies without losing incoming data or corrupting outgoing data.

- The 82557 XMT FIFO Threshold allows the transmit start threshold to be tuned to eliminate underruns while concurrent transmits are being performed.

- The FIFO subsection allows extended PCI 0

Wait State burst accesses to or from the 82557

for both RCV and XMT frames, since the transfer

is to the FIFO storage area as opposed to

directly to the serial link.

- Transmissions resulting in errors (CDT, Underrun) are retransmitted directly from the 82557 FIFO, increasing performance and eliminating the need to reaccess this data from the host system.

- Incoming Runt RCV Frames (less than the legal minimum frame size) can be discarded automatically by the 82557 without transferring this faulty data to the host system.

# 3.3. 10/100 Mbps Serial CSMA/CD Unit Overview

The CSMA/CD unit of the 82557 allows it to be connected to either a 10 or 100 Mbps Ethernet network. The 82557 interfaces to either an IEEE 802.3 10/100 Mbps MII compatible PHY device or a 10 Mbps-only IEEE 802.3 PHY. In the case of the MII compatible PHY, the 82557 can switch automatically between 10 or 100 Mbps operation depending on the speed of the network. The CSMA/CD unit performs all of the functions of the 802.3 protocol such as frame formatting, frame stripping, collision handling, deferral to link traffic, etc. The CSMA/CD unit can also be placed in a Full Duplex mode which allows for simultaneous transmission and reception of frames. The CSMA/CD unit accepts data from the 82557 XMT FIFO and converts it to either serial or nibble-wide (MII Compatible mode) data for transmission on the link. During reception, the CSMA/CD unit converts data from either serial or nibble-wide data to a byte-wide format and transfers it to the RCV FIFO of the 82557. The CSMA/CD unit contains a Management Data Interface (MDI) to an MII compliant PHY. This allows control and status parameters to be passed between the 82557 and the PHY (parameters specified by software) by one serial pin and a clocking pin, reducing the number of control pins needed for PHY mode control.

# 4.0. THE 82557 HARDWARE INTERFACE

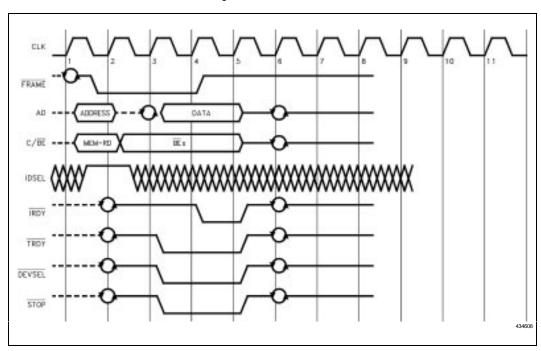

#### 4.1. PCI Bus Interface

The PCI bus interface enables the 82557 to interact with the host system via the PCI bus. It provides the control, address and data interface to implement a PCI compliant device. The 82557 operates as both a master and slave on the PCI bus. As a master, the 82557 interacts with the system main memory to access data for transmission or deposit received data

As a slave, some 82557 control structures are accessed by the host CPU which reads or writes to these on-chip registers. The CPU provides the 82557 with the necessary action commands, control commands and pointers which enable the 82557 to process RCV and XMT data. The PCI bus interface also provides the means for configuring PCI parameters in the 82557. Refer to the PCI Bus Interface Specification for more details specific to the PCI bus.

### 4.1.1. PCI CONFIGURATION

The configuration process in a PCI system starts before anything else. The 82557 is actually disconnected from the PCI bus until it is configured. At this stage it responds to configuration cycles only. This subsection provides a detailed description of the PCI configuration process from software and hardware points of view. Specifically, it defines the programming model and usage rules for the configuration register space of the 82557.

The 82557 supports all mandatory required registers along with specific registers that are needed for its operation. Mainly, it implements several Base Address registers. These registers and their purpose will be described in detail later on. For more concise information refer to the *PCI System Design Guide*.

# 4.1.1.1. PCI Configuration Space Organization

The organization of configuration space registers as defined in the PCI specification is shown Table 1.

This region consists of fields that uniquely identify the 82557 and allow it to be generically controlled. The This region consists of fields that uniquely identify the 82557 treats configuration space write operations to reserved registers as no-ops (the data written is ignored). Read accesses to reserved or undefined registers will always return a data value of all zeros. For all accesses to the PCI Configuration Registers, the 82557 will disconnect from the bus following each access. In other words, no burst accesses may be made to these registers.

Table 1 shows the layout of the 64 byte predefined header portion of the 256-byte configuration space that every PCI device must support. These registers are known as the PCI Configuration Registers in the 82557. Devices must place any necessary device specific registers only in locations 64 through 255. Currently, the 82557 does not implement any register beyond the 64 byte predefined header portion. All multibyte numeric fields follow *little-endian* ordering. That is, lower addresses contain the least significant parts of the field. Software must take care to deal correctly with bit-encoded fields that have some bits reserved for future use.

On reads, software must use appropriate masks to extract the defined bits, and may not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and the data then written back. Section 4.1.2 describes the registers in the predefined header portion of the configuration space. It also specifies which registers are reserved and which ones are implemented.

The predefined header portion of the configuration space is divided into two parts. The first 16 bytes are defined the same for all types of PCI compliant devices. The 82557 B-step, as a PCI compliant device, supports the Vendor ID, Device ID, Command and Status fields in the header. The C-step (available in March 1997) will also include the Sub-vendor ID and Device ID. Implementation of the other registers is optional (i.e., they can be treated as reserved registers). The specific implementation of these resisters in the 82557 is described in Section 4.1.2.

Table 1. PCI Configuration Registers

| Device I  | D                                | Vendor ID             |                 | 00h |  |

|-----------|----------------------------------|-----------------------|-----------------|-----|--|

| Status    |                                  | Command               |                 | 04h |  |

|           | Class Code                       |                       | Revision ID     | 08h |  |

| BIST      | Header Type                      | Latency Timer         | Cache Line Size | 0Ch |  |

|           | CSR Mem Mappe                    | ed Base Addr Register |                 | 10h |  |

|           | CSR I/O Mapped                   | d Base Addr Register  |                 | 14h |  |

|           | Flash Mem Mappe                  | ed Base Addr Register |                 | 18h |  |

|           | Reserved Base Addr Register      |                       |                 |     |  |

|           | Reserved Base Addr Register      |                       |                 |     |  |

|           | Reserved Base Addr Register      |                       |                 |     |  |

|           | Re                               | served                |                 | 28h |  |

| SubSyster | SubSystem ID SubSystem Vendor ID |                       |                 |     |  |

|           | Expansion ROM Base Addr          |                       |                 |     |  |

|           | Reserved                         |                       |                 |     |  |

|           | Reserved                         |                       |                 |     |  |

| Max_Lat   | Min_Gnt                          | Interrupt Pin         | Interrupt Line  | 3Ch |  |

# 4.1.1.2. PCI Configuration Registers

This section lists and describes all PCI registers defined in the predefined header portion of the configuration space that are supported and implemented in the 82557. All reserved registers are also specified.

Configuration space is intended for configuration, initialization, and catastrophic error handling functions. Its use should be restricted to initialization software and error handling software. All operational software must continue to use I/O and/or memory space accesses to manipulate device registers. The

PCI configuration registers are described while partitioned into several groups according to their functionality.

# **Device Identification Registers**

Five fields (seven in the C-step part) in the predefined header deal with device identification. The 82557, as a PCI compliant device, implements them as required. These registers (fields) enable generic configuration software to easily determine what devices are available on the system's PCI bus. All of these registers are read-only. The description of their functionality and their assigned value in the 82557 is given in Table 2. Their location (offset) in the PCI configuration space is given in Table 1.

Table 2. Device Identification Registers

| Register    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vendor ID   | This field identifies the manufacturer of the device. Valid vendor identifiers are allocated by the PCI SIG to ensure uniqueness. The vendor ID value for the 82557 is always 8086 and is read-only.                                                                                                                                                                                                                                                                                                                       |

| Device ID   | This field identifies the particular device. This identifier is allocated by the vendor. The device ID for the 82557 is 1229 and is read-only.                                                                                                                                                                                                                                                                                                                                                                             |

| Revision ID | This read-only register specifies the 82557 stepping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Header Type | This byte identifies the layout of bytes 10h through 3Fh in configuration space and also whether or not the device contains multiple functions. The 82557 Header Type of 00h specifies the layout shown in Figure 3 and indicates a single function device. This field is read-only.                                                                                                                                                                                                                                       |

| Class Code  | The Class Code register is read-only and is used to identify the generic function of the device and (in some cases) a specific register-level programming interface. The register is broken into three byte-size fields. The upper byte, 02h is a base class code and specifies the 82557 as a Network Controller. The middle byte is a sub-class code, 00h which specifies Ethernet Controller. The lower byte identifies a specific register-level programming interface and the 82557 always returns 00h in this field. |

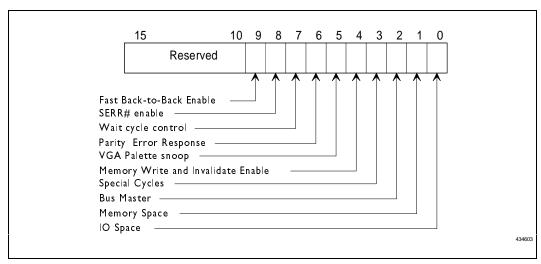

## **PCI Command Register**

The PCI Command Register (04h) provides control over the 82557's ability to generate and respond to PCI cycles. When a 0 is written to this register, the 82557 is logically disconnected from the PCI bus for

all accesses except configuration accesses. Figure 2 shows the layout of the register and Table 3 explains the meanings of the different bits in the Command register. Table 3 also gives the default value of this register upon power up and the specific implementation of individual bits in the 82557 (i.e., R/O or R/W).

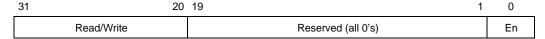

Figure 2. PCI Command Register Layout

Table 3. PCI Command Register Bits

| Bit # | Bit Name                 | Description                                                                                                                                                                                                                                                                                                                                                     |

|-------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | IO Space                 | This bit controls a device's response to I/O space accesses. A value of 0 disables the device response. A value of 1 allows the device to respond to I/O space accesses. The specific implementation of this bit in the 82557 is configurable with default value 0.                                                                                             |

| 1     | Mem Space                | This bit controls a device's response to memory space accesses. A value of 0 disables the device response. A value of 1 allows the device to respond to memory space accesses. This bit is configurable in the 82557 with a default value 0.                                                                                                                    |

| 2     | Bus Master               | This bit controls a device's ability to act as a master on the PCI bus. A value of 0 disables the device from generating PCI accesses. A value of 1 allows the device to behave as a bus master. This bit is configurable in the 82557 with a default value 0.                                                                                                  |

| 3     | Special Cycle            | This bit controls a device's action on Special Cycle operations. A value of 0 causes the device to ignore all Special Cycle operations. This bit is always set to 0 in the 82557.                                                                                                                                                                               |

| 4     | Mem WR & Invalidate En   | This is an enable bit for using the Memory Write and Invalidate command. This bit is always set to 0 in the 82557 (disabled).                                                                                                                                                                                                                                   |

| 5     | VGA Palette Snoop        | This bit controls how VGA compatible devices handle accesses to their palette registers. This bit is always set to a 0 in the 82557 (disabled).                                                                                                                                                                                                                 |

| 6     | Parity Error Response    | This bit controls the 82557's response to parity errors. When the bit is set, the 82557 takes its normal action when a parity error is detected. When the bit is reset, the 82557 ignores any parity errors that it detects and continues normal operation. This bit must be set to 0 after RST#. This bit is configurable in the 82557 with a default value 0. |

| 7     | Wait Cycle Control       | This bit, when set to a 1, is used to control whether or not a device does address/data stepping. This bit is always set to 0 in the 82557 (disabled).                                                                                                                                                                                                          |

| 8     | Serr Enable              | This bit is an enable bit for the SERR# driver. A value of 0 disables the SERR# driver. A value of 1 enables the SERR# driver. This bit (and bit 6, PERR# Enable) must be on to report address parity errors. This bit is configurable in the 82557 with a default value of 0.                                                                                  |

| 9     | Fast Back to Back Enable | This bit controls whether or not a master can do fast back-to-back transactions to different devices. This bit is set to a 0 in the 82557, fast back-to-back transactions are only allowed to the same agent.                                                                                                                                                   |

| 10-15 | Reserved                 | Reserved. These bits are hardwired to 0 in the 82557.                                                                                                                                                                                                                                                                                                           |

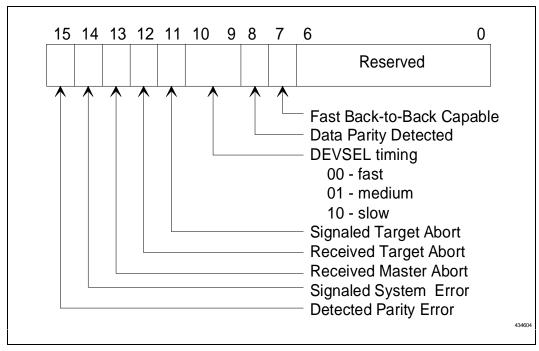

### **PCI Status Register**

The PCI Status Register is used to record status information for PCI bus related events. The definition of each of the bits is given in Table 4 and the layout of the register is shown in Figure 3. Reads to this

register behave normally. Writes are slightly different in that bits can be reset, but not set. A bit is reset whenever the register is written, and the data in the corresponding bit location is a 1. For instance, to clear bit 14 and not affect any other bits, write the value 0100\_0000\_0000\_0000b to the register.

Figure 3. PCI Status Register Layout

Table 4. PCI Status Register Bits

| Bit # | Bit Location              | Description                                                                                                                                                                                                                                                                                                                        |

|-------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-6   | Reserved                  | These bits are hardwired to 0 in the 82557.                                                                                                                                                                                                                                                                                        |

| 7     | Fast Back to Back Capable | This read-only bit indicates whether or not the target is capable of accepting fast back-to-back transactions when the transactions are not to the same agent. The value of this bit in the 82557 is 1 (Fast Back to Back Capable).                                                                                                |

| 8     | Data Parity Detected      | This bit is set when three conditions are met: 1) the bus agent asserted PERR# itself or observed PERR# asserted; 2) the agent setting the bit acted as the bus master for the operation in which the error occurred; 3) the Parity Error Response bit (Command Register) is set. The initial value of this bit in the 82557 is 0. |

| 9-10  | DEVSEL# Timing            | These bits encode the timing of DEVSEL#. There are three allowable timings for assertion of DEVSEL#. These are encoded as 00b for fast, 01b for medium, and 10b for slow (11b is reserved). The value of these bits are always set to 01 (medium).                                                                                 |

| 11    | Signaled Target Abort     | This bit must be set by a target device whenever it terminates a transaction with target-abort. The value of this bit is always 0.                                                                                                                                                                                                 |

| 12    | Received Target Abort     | This bit must be set by a master device whenever its transaction is terminated with target-abort. The initial value of this bit in the 82557 is 0.                                                                                                                                                                                 |

| 13    | Received MasterAbort      | This bit must be set by a master device whenever its transaction (except for Special Cycle) is terminated with master-abort. The initial value of this bit in the 82557 is 0.                                                                                                                                                      |

| 14    | Signaled SystemError      | This bit must be set whenever the device asserts SERR#. The initial value of this bit in the 82557 is 0.                                                                                                                                                                                                                           |

| 15    | Detected Parity Error     | This bit must be set by the device whenever it detects a parity error, even if parity error handling is disabled (as controlled by bit 6 in the Command register). The initial value of this bit in the 82557 is 0.                                                                                                                |

## Miscellaneous PCI Configuration Registers

This section describes the registers that are device independent and only need to be implemented by

devices that provide the described function. The specific implementation of each register for the 82557 is provided in Table 5.

Table 5. Miscellaneous PCI Configuration Bits

| Register                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache Line Size           | This register is not implemented in the 82557. The value of this field is fixed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Latency Timer             | The 82557, as a master device, implements this register to limit the size of very long burst cycles. The initial value is 0 and is then programmed by system BIOS at initialization time.                                                                                                                                                                                                                                                                                                                               |

| Built-in Self Test (BIST) | This optional register is used for control and status of BIST. The 82557 will not provide PCI BIST and the value of this field is always set to 0.                                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt Line            | The Interrupt Line register is an 8-bit register used to communicate interrupt line routing information. This register is configurable in the 82557. POST software will write the routing information into this register as it initializes and configures the system. The value in this register defines which input of the system interrupt controller(s) the device's interrupt pin is connected to. Device drivers and operating systems can then use this information to determine priority and vector information. |

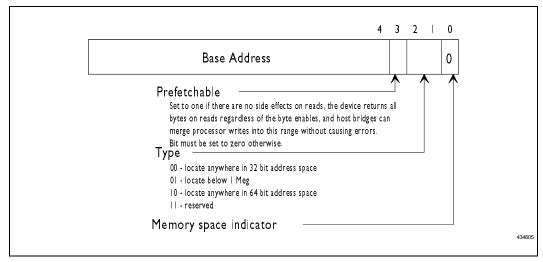

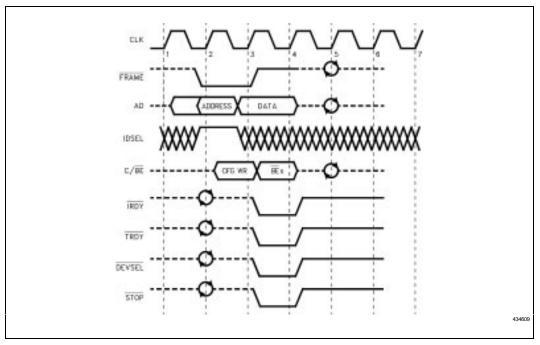

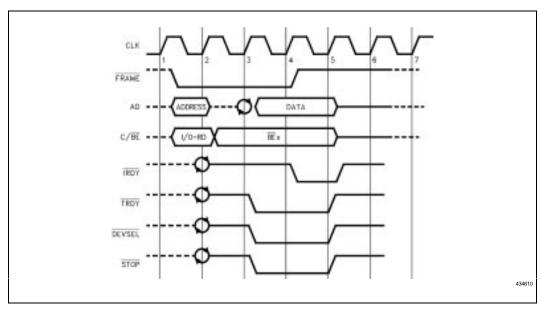

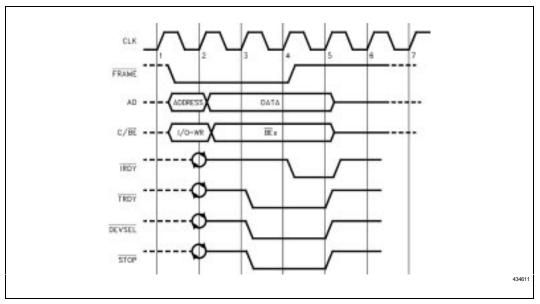

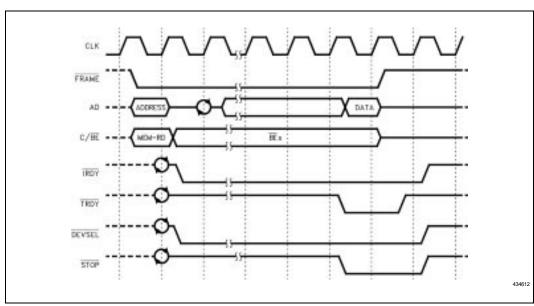

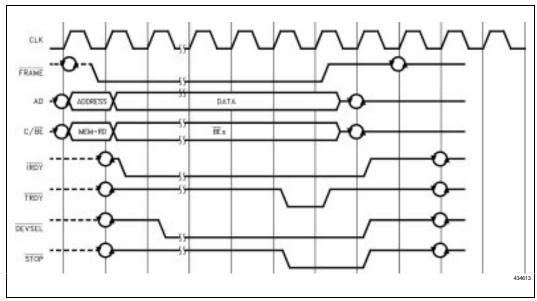

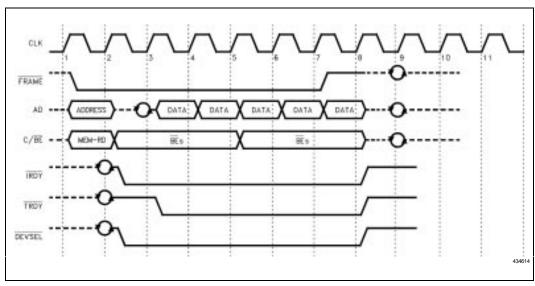

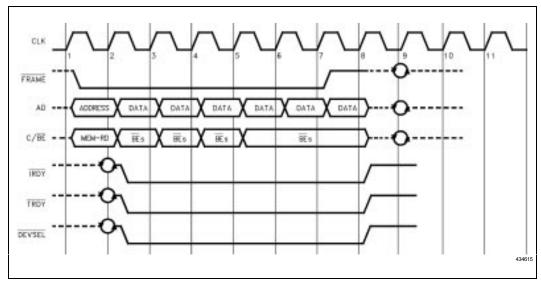

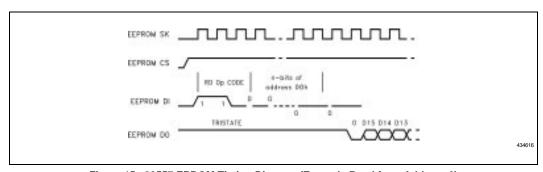

| Interrupt Pin             | The Interrupt Pin register tells which interrupt pin the device (or device function) uses. This eight bit register is always set to a 1 in the 82557, indicating INTA# is used.                                                                                                                                                                                                                                                                                                                                         |