# i960<sup>®</sup> Rx I/O PROCESSOR SPECIFICATION UPDATE

Release Date: March, 1997

Order Number: 272918-007

The  $i960^{@}$  Rx I/O Processor may contain design defects or errors known as errata. Characterized errata that may cause the  $i960^{@}$  Rx I/O Processor's behavior to deviate from published specifications are documented in this specification update.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

\*Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect IL 60056-7641

or call in North America 1-800-879-4683, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other countries 708-296-9333

Copyright © 1997, INTEL CORPORATION

| REVISION HISTORY             | 1  |

|------------------------------|----|

| PREFACE                      | 2  |

| SUMMARY TABLE OF CHANGES     | 4  |

| IDENTIFICATION INFORMATION   | 12 |

| ERRATA                       | 13 |

| SPECIFICATION CHANGES        | 25 |

| SPECIFICATION CLARIFICATIONS | 30 |

| DOCUMENTATION CHANGES        | 35 |

# **REVISION HISTORY**

| Rev. Date | Version | Description                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3/12/97   | 007     | Added specification clarification 8. In SUMMARY TABLE OF CHANGES Errata table item 10, added "X" for 80960RP 33/3.3 and the 80960RD 66/3.3 A0 step.                                                                                                                                                                                                                      |  |  |  |  |

| 2/10/97   | 006     | Added errata items 21, 22. Added specification change items 7, 8, 9, 10, 11 (the previous specification change item #6 is now specification clarification item 5). Added specification clarification items 6, 7. Changed the status of errata items 15, 19, 20. Changed the stepping information for specification change item 4. Modified documentation change item 39. |  |  |  |  |

|           |         | Added new stepping information; see IDENTIFICATION INFORMATION. References to "80960RP" have changed to 80960RP 33/3.3, 80960RP 33/5.0, 80960RD 66/3.3, where appropriate, to reflect the new steppings. See SUMMARY TABLE OF CHANGES.                                                                                                                                   |  |  |  |  |

|           |         | In the ERRATA descriptions, the "Status" heading has been removed. Refer to the Errata table in SUMMARY TABLE OF CHANGES for status.                                                                                                                                                                                                                                     |  |  |  |  |

| 1/15/97   | 005     | Added errata items 18, 19. Added three documentation changes. See Summary Table of Changes for complete list.                                                                                                                                                                                                                                                            |  |  |  |  |

| 12/04/96  | 004     | Added errata items 14, 15, 16, 17. Added specification clarification item 5. Added several documentation changes. See Summary Table of Changes for complete list.                                                                                                                                                                                                        |  |  |  |  |

| 11/01/96  | 003     | Added errata items 12, 13. Changed the status of errata item 2 from Eval to Fix. Added Specification Change item 5. Added several documentation changes. See Summary Table of Changes for complete list.                                                                                                                                                                 |  |  |  |  |

|           |         | Changed numbering sequences for Revision History, Errata, Specification Changes, Specification Clarifications and Document Changes.                                                                                                                                                                                                                                      |  |  |  |  |

|           |         | Added subheadings under Document Changes to separate individual document types (i.e., User's Manual, Addendum, etc.).                                                                                                                                                                                                                                                    |  |  |  |  |

| 9/6/96    | 002     | Added errata items 9, 10, 11. Added information for the A-1 stepping. Added Specification Change 4.                                                                                                                                                                                                                                                                      |  |  |  |  |

| 7/15/96   | 001     | This is the new Specification Update document. It contains all identified errata published prior to this date.                                                                                                                                                                                                                                                           |  |  |  |  |

272918-007 March, 1997 1 of 62

#### PREFACE

As of July, 1996, Intel has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### Affected Documents/Related Documents

| Title                                             | Order      |

|---------------------------------------------------|------------|

| i960 <sup>®</sup> RP Microprocessor User's Manual | 272736-001 |

| i960® RP I/O Processor at 5 Volts Data Sheet      | 272737-003 |

| i960® RP/RD I/O Processor at 3.3 Volts Data Sheet | 273001-001 |

#### Nomenclature

**Errata** are design defects or errors. These may cause the published (component, board, system) behavior to deviate from published specifications. Hardware and software designed to be used with any component, board, and system must consider all errata documented.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# intها

#### 80960Rx SPECIFICATION UPDATE

#### NOTE:

Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

#### SUMMARY TABLE OF CHANGES

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the 80960Rx product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### Codes Used in Summary Table

## Stepping

X: Errata exists in the stepping indicated. Specification Change

or Clarification that applies to this stepping.

(No mark)

or (Blank box): This erratum is fixed in listed stepping or specification change

does not apply to listed stepping.

Page

(Page): Page location of item in this document.

Status

Doc: Document change or update will be implemented.

Fix: This erratum is intended to be fixed in a future step of the com-

ponent.

Fixed: This erratum has been previously fixed. NoFix: There are no plans to fix this erratum.

Eval: Plans to fix this erratum are under evaluation.

Row

Change bar to left of table row indicates this erratum is either

new or modified from the previous version of the document.

# Errata (Sheet 1 of 2)

|      |     | Steppi       | ng                          |      |                                                                                                                                                                 |                                                                                                                                                                                                     |  |

|------|-----|--------------|-----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Item |     | 50RP<br>/5.0 | 80960<br>RP/RD<br>33/66/3.3 | Page | Status                                                                                                                                                          | Status ERRATA                                                                                                                                                                                       |  |

|      | A-0 | A-1          | A-0                         |      |                                                                                                                                                                 |                                                                                                                                                                                                     |  |

| 1    | Χ   | Х            |                             | 13   | Fix                                                                                                                                                             | Loss of local grant signal during an expansion ROM access                                                                                                                                           |  |

| 2    | Χ   | Х            |                             | 13   | Fix                                                                                                                                                             | Byte enables, BE1:0#, can cause hold violations to flash memory                                                                                                                                     |  |

| 3    | Х   | X            |                             | 14   | Fix                                                                                                                                                             | Fix The loss of HOLD on the 80960 local bus from an external bus master during a DRAM refresh cycle could cause bus ownership issues with the primary ATU, the Messaging Unit, or the expansion ROM |  |

| 4    | Х   | Х            |                             | 14   | Fix                                                                                                                                                             | Unaligned DMA read transfers could prevent further operation of DMA Unit                                                                                                                            |  |

| 5    | Χ   | Х            |                             | 15   | Fix                                                                                                                                                             | Fix Bridge Control Register can only be written as a 16-bit value                                                                                                                                   |  |

| 6    | Χ   | Х            | Х                           | 15   | NoFix Parity checking for inbound PCI address cycles is always enabled for the ATU                                                                              |                                                                                                                                                                                                     |  |

| 7    | Х   | Х            |                             | 16   | Fix                                                                                                                                                             | ·                                                                                                                                                                                                   |  |

| 8    | Х   | Х            |                             | 16   | Fix PCI Master Parity Error bits set in Bridge Interrupt Status Registers regardless of whether parity checking is enabled                                      |                                                                                                                                                                                                     |  |

| 9    | Х   |              |                             | 17   | Fix                                                                                                                                                             | 1 7 3                                                                                                                                                                                               |  |

| 10   | Х   |              | Х                           | 17   | Fix                                                                                                                                                             | Intermittent ONCE Mode upon power-up                                                                                                                                                                |  |

| 11   | Х   | Х            |                             | 18   | Fix ATU lockup condition under simultaneous outbound read data and inbound write data through the inbound data queue                                            |                                                                                                                                                                                                     |  |

| 12   | Х   | Х            |                             | 18   | Fix PCI-to-PCI bridge can corrupt data during Memory Write and Invalidate cycles that insert IRDY# wait states during data-data transfers                       |                                                                                                                                                                                                     |  |

| 13   | Х   | Х            |                             | 19   | Fix Using the Messaging Unit circular queues with more than one recovery wait state on the local bus can cause primary Address Translation Unit data corruption |                                                                                                                                                                                                     |  |

# Errata (Sheet 2 of 2)

|      |     | Steppi       | ng                          |      |                                                                                                                                                                                                       |                                                                                                                          |  |

|------|-----|--------------|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Item |     | 60RP<br>/5.0 | 80960<br>RP/RD<br>33/66/3.3 | Page | Status                                                                                                                                                                                                | ERRATA                                                                                                                   |  |

|      | A-0 | A-1          | A-0                         |      |                                                                                                                                                                                                       |                                                                                                                          |  |

| 14   | Х   | Х            |                             | 20   | Fix                                                                                                                                                                                                   | Access to non-existent DRAM causes incorrect error reporting                                                             |  |

| 15   | Х   | Х            | X                           | 20   | NoFix                                                                                                                                                                                                 | Fix Address Translation Unit write and Messaging Unit queue port write may get out of order on the 80960 local bus       |  |

| 16   | Х   | Х            |                             | 21   | Fix                                                                                                                                                                                                   | Using multiple DMA channels that perform unaligned transfers can cause a DMA channel performing a read to stop operating |  |

| 17   | Х   | Х            |                             | 22   | Fix                                                                                                                                                                                                   | Fix Messaging Unit logs multiple interrupt sources when using the index registers                                        |  |

| 18   | Х   | Х            | Х                           | 24   | Eval                                                                                                                                                                                                  | DMA Descriptors appended to the end of a chain may not execute                                                           |  |

| 19   | Х   | Х            | Х                           | 23   | NoFix                                                                                                                                                                                                 | Downstream exclusive read transaction through multiple bridges may cause a deadlock condition                            |  |

| 20   | Х   | Х            | Х                           | 23   | Fix                                                                                                                                                                                                   | Inbound ATU PCI read issue with retried completion cycles                                                                |  |

| 21   | Х   | Х            | Х                           | 24   | Fix                                                                                                                                                                                                   | Null writes (BE3:0# deasserted) to the MU Inbound and Outbound Queue Ports corrupt the corresponding queue pointer       |  |

| 22   | Х   | Х            |                             | 24   | corresponding queue pointer  Fix PCI-to-PCI Bridge Unit can corrupt data during Memory Write cycles when wait states are inserted simultaneously on both the primary an secondary sides of the bridge |                                                                                                                          |  |

# Specification Changes

|      | Stepping |              |                                 |      |        |                                                                                                                                              |  |

|------|----------|--------------|---------------------------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Item |          | 50RP<br>/5.0 | 80960<br>RP/RD<br>33/66/<br>3.3 | Page | Status | SPECIFICATION CHANGES                                                                                                                        |  |

|      | A-0      | A-1          | A-0                             |      |        |                                                                                                                                              |  |

| 1    | Х        | Х            |                                 | 25   | Doc    | PCI Interrupt Routing Select Register (PIRSR) Polarity                                                                                       |  |

| 2    | Χ        | X            | Х                               | 25   | Doc    | Asynchronous clocking mode not supported                                                                                                     |  |

| 3    | Х        | Х            | Х                               | 25   | Doc    | The MU interlock mechanism remains enabled for APIC registers when the APIC is disabled                                                      |  |

| 4    |          | Х            | Х                               | 26   | Doc    | Incorrect BIOS access of block size from Base Address Registers                                                                              |  |

| 5    | Х        | Х            | Х                               | 26   | Doc    | ATU Configuration Register Bit 12 Definition is Changed                                                                                      |  |

| 6    |          |              |                                 | 27   | Doc    | Multiple reads of the Base Address Register after writing all 1's will return different values (See Specification Clarification Item #5)     |  |

| 7    |          |              | Х                               | 27   | Doc    | Additional devices can be configured as public or private on the secondary PCI bus by programming the Secondary IDSEL Select Register (SISR) |  |

| 8    |          |              | Х                               | 27   | Doc    | PCI Interrupt Routing Select Register (PIRSR) now supports individual routing of each XINT3:0#                                               |  |

| 9    |          |              | Х                               | 27   | Doc    | The Memory Bank Extended MWE3:0# bits in the Memory Bank Control Register can provide one clock of address hold time during write cycles     |  |

| 10   |          |              | Х                               | 28   | Doc    | Mask bits added for all PCI-PCI bridge error conditions which may cause an NMI# to the i960 core processor                                   |  |

| 11   |          |              | Х                               | 29   | Doc    | Multiple reads of the Base Address Register, after writing all 1's, returns the limit register value until rewritten                         |  |

# Specification Clarifications

|      | ,   | Stepping     | 9                               |      |        |                                                                                                |  |

|------|-----|--------------|---------------------------------|------|--------|------------------------------------------------------------------------------------------------|--|

| Item |     | 60RP<br>/5.0 | 80960<br>RP/RD<br>33/66/<br>3.3 | Page | Status | SPECIFICATION CLARIFICATIONS                                                                   |  |

|      | A-0 | A-1          | A-0                             |      |        |                                                                                                |  |

| 1    | Х   | Х            |                                 | 30   | Doc    | Five IDSEL lines for the secondary PCI bus are not enabled                                     |  |

| 2    | Х   | Х            | Х                               | 30   | Doc    | How to use the Data Enable (DEN#) Signal with an In-Circuit Emulator                           |  |

| 3    | Х   | Х            | Х                               | 31   | Doc    | Accessing 80960Rx MMRs via the primary PCI bus                                                 |  |

| 4    | Х   | Х            | Х                               | 32   | Doc    | Parity on data cycles not checked before delayed write completion cycles are accepted          |  |

| 5    | Х   | Х            |                                 | 32   | Doc    | Multiple reads of the Base Address Register after writing all 1's will return different values |  |

| 6    | Х   | Х            | Х                               | 32   | Doc    |                                                                                                |  |

| 7    | Х   | Х            | Х                               | 33   | Doc    |                                                                                                |  |

| 8    | Χ   | Χ            | Χ                               | 34   | Doc    | Parity error reporting during configuration cycles                                             |  |

# **Documentation Changes** (Sheet 1 of 4)

| Item | Document<br>Revision | Page | DOCUMENTATION CHANGES                |  |

|------|----------------------|------|--------------------------------------|--|

| 1.   | 272736-001           | 35   | Section 8.2.2, Page 8-16             |  |

| 2.   | 272736-001           | 35   | Section 8.3.3, Page 8-27             |  |

| 3.   | 272736-001           | 35   | Section 8.4.7, Page 8-36             |  |

| 4.   | 272736-001           | 36   | Section 8.4.7, Page 8-37, Table 8-10 |  |

| 5.   | 272736-001           | 36   | Section 9.10.8, Page 9-34            |  |

| 6.   | 272736-001           | 36   | Section 11.2.1, Page 11-3            |  |

| 7.   | 272736-001           | 36   | Section 11.2.8, Page 11-6            |  |

| 8.   | 272736-001           | 37   | Section 11.4, Page 11-12             |  |

| 9.   | 272736-001           | 37   | Section 11.6, Page 11-24             |  |

| 10.  | 272736-001           | 37   | Section 11.6.1, Page 11-24           |  |

# **Documentation Changes** (Sheet 2 of 4)

| Item | Document<br>Revision | Page | DOCUMENTATION CHANGES                                   |  |

|------|----------------------|------|---------------------------------------------------------|--|

| 11.  | 272736-001           | 37   | Section 13.3.7, Page 13-18                              |  |

| 12.  | 272736-001           | 37   | Section 13.6, Page 13-24                                |  |

| 13.  | 272736-001           | 37   | Section 13.6.1, Page 13-26                              |  |

| 14.  | 272736-001           | 38   | Section 14.4.1, Page 14-8, Table 14-2                   |  |

| 15.  | 272736-001           | 38   | Section 14.4.5, Page 14-14, Figure 14-5                 |  |

| 16.  | 272736-001           | 38   | Section 14.4.5, Page 14-15, Figure 14-6                 |  |

| 17.  | 272736-001           | 38   | Section 14.4.5, Page 14-16, Figure 14-7                 |  |

| 18.  | 272736-001           | 39   | Section 14.4.5, Page 14-16, Figure 14-8                 |  |

| 19.  | 272736-001           | 39   | Section 14.4.5, Page 14-17, Figure 14-9                 |  |

| 20.  | 272736-001           | 39   | Section 14.5, Page 14-18, Table 14-6                    |  |

| 21.  | 272736-001           | 39   | Section 14.5.1, Page 14-22, Table 14-8                  |  |

| 22.  | 272736-001           | 39   | Section 14.5.4, Page 14-24, Table 14-9                  |  |

| 23.  | 272736-001           | 40   | Section 14.5.6, Page 14-27, Table 14-11                 |  |

| 24.  | 272736-001           | 40   | Section 14.5.7, Page 14-29, Table 14-12                 |  |

| 25.  | 272736-001           | 41   | Section 14.5.8, Page 14-31, Table 14-13                 |  |

| 26.  | 272736-001           | 41   | Section 14.6.2, Page 14-33, Table 14-15                 |  |

| 27.  | 272736-001           | 41   | Section 14.7.2, Page 14-38 and 39, Figures 14-17 and 18 |  |

| 28.  | 272736-001           | 41   | Section 15.5.2.1, Page 15-12                            |  |

| 29.  | 272736-001           | 41   | Section 15.5.6, Page 15-16                              |  |

| 30.  | 272736-001           | 41   | Section 15.5.6, Page 15-19 and 15-20, Table 15-6        |  |

| 31.  | 272736-001           | 41   | Section 15.6.2.1, Page 15-22                            |  |

| 32.  | 272736-001           | 41   | Section 15.6.2.2, Page 15-23                            |  |

| 33.  | 272736-001           | 41   | Section 15.12.5, Page 15-37                             |  |

| 34.  | 272736-001           | 42   | Section 15.13, Page 15-37                               |  |

| 35.  | 272736-001           | 42   | Section 15.13, Page 15-38, Figure 15-8                  |  |

| 36.  | 272736-001           | 42   | Section 15.13.4, Page 15-42, Table 15-16                |  |

| 37.  | 272736-001           | 43   | Section 15.13.7, Page 15-44, Table 15-19                |  |

| 38.  | 272736-001           | 43   | Section 15.13.16, Page 15-50, Table 15-28               |  |

| 39.  | 272736-001           | 43   | Section 15.13.23, Page 15-54, Table 15-35               |  |

| 40.  | 272736-001           | 48   | Section 15.13.23, Pages 15-54, Table 15-34              |  |

| 41.  | 272736-001           | 48   | Section 16.1, Page 16-2                                 |  |

# **Documentation Changes** (Sheet 3 of 4)

| Item | Document<br>Revision | Page | DOCUMENTATION CHANGES                     |  |

|------|----------------------|------|-------------------------------------------|--|

| 42.  | 272736-001           | 48   | Section 16.2.1, Page 16-5, Figure 16-2    |  |

| 43.  | 272736-001           | 48   | Section 16.2.1, Page 16-5                 |  |

| 44.  | 272736-001           | 49   | Section 16.2.2, Page 16-7                 |  |

| 45.  | 272736-001           | 49   | Section 16.2.2, Page 16-8                 |  |

| 46.  | 272736-001           | 49   | Section 16.2.3, Page 16-8                 |  |

| 47.  | 272736-001           | 49   | Section 16.2.6.1, Page 16-10              |  |

| 48.  | 272736-001           | 50   | Section 16.2.6.1, Page 16-11, Figure 16-4 |  |

| 49.  | 272736-001           | 50   | Section 16.2.6.1, Page 16-12              |  |

| 50.  | 272736-001           | 50   | Section 16.2.6.1, Page 16-13, Figure 16-5 |  |

| 51.  | 272736-001           | 50   | Section 16.2.6.2, Page 16-14              |  |

| 52.  | 272736-001           | 50   | Section 16.5, Page 16-18, Figure 16-7     |  |

| 53.  | 272736-001           | 50   | Section 16.5.1, Page 16-18                |  |

| 54.  | 272736-001           | 50   | Section 16.6, Page 16-20, Table 16-3      |  |

| 55.  | 272736-001           | 51   | Section 16.7, Page 16-24                  |  |

| 56.  | 272736-001           | 51   | Section 16.7, Page 16-25, Figure 16-8     |  |

| 57.  | 272736-001           | 51   | Section 16.7, Page 16-26, Table 16-8      |  |

| 58.  | 272736-001           | 51   | Section 16.7.2, Page 16-29, Table 16-11   |  |

| 59.  | 272736-001           | 51   | Section 16.7.4, page 16-31                |  |

| 60.  | 272736-001           | 51   | Section 16.7.7, Page 16-33, Table 16-16   |  |

| 61.  | 272736-001           | 51   | Section 16.7.8, Page 16-33, Table 16-17   |  |

| 62.  | 272736-001           | 51   | Section 16.7.9, Page 16-34, Table 16-18   |  |

| 63.  | 272736-001           | 51   | Section 16.7.11, Page 16-35               |  |

| 64.  | 272736-001           | 52   | Section 16.7.14.1, Page 16-38             |  |

| 65.  | 272736-001           | 52   | Section 16.7.19, Page 16-43, Table 16-30  |  |

| 66.  | 272736-001           | 52   | Section 16.7.21, Page 16-44               |  |

| 67.  | 272736-001           | 52   | Section 16.7.30, Page 16-50               |  |

| 68.  | 272736-001           | 53   | Section 16.7.32, Page 16-51, Table 16-43  |  |

| 69.  | 272736-001           | 56   | Section 16.7.33, page 16-53, Table 16-44  |  |

| 70.  | 272736-001           | 56   | Section 16.7.33, Page 16-54, Table 16-44  |  |

| 71.  | 272736-001           | 56   | Section 16.7.34, page 16-54, Table 16-45  |  |

| 72.  | 272736-001           | 56   | Section 16.7.34, Page 16-55, Table 16-45  |  |

# **Documentation Changes** (Sheet 4 of 4)

| Item | Document<br>Revision | Page | DOCUMENTATION CHANGES                    |  |  |

|------|----------------------|------|------------------------------------------|--|--|

| 73.  | 272736-001           | 56   | Section 16.7.35, Page 16-56, Table 16-46 |  |  |

| 74.  | 272736-001           | 56   | Section 16.7.36, page 16-57              |  |  |

| 75.  | 272736-001           | 57   | Section 16.7.37, page 16-57, Table 16-47 |  |  |

| 76.  | 272736-001           | 57   | Section 16.7.39, Page 16-58              |  |  |

| 77.  | 272736-001           | 57   | Section 16.7.40, Page 16-59              |  |  |

| 78.  | 272736-001           | 57   | Section 16.7.41, Page 16-59 and 60       |  |  |

| 79.  | 272736-001           | 58   | Section 16.7.41.1, Page 16-39            |  |  |

| 80.  | 272736-001           | 58   | Section 16.7.42, Page 16-60              |  |  |

| 81.  | 272736-001           | 58   | Section 17.7.20, Page 17-30, Figure 17-3 |  |  |

| 82.  | 272736-001           | 58   | Section 18.2.3, Page 18-6                |  |  |

| 83.  | 272736-001           | 59   | Section 18.3.2, Page 18-11               |  |  |

| 84.  | 272736-001           | 59   | Section 18.3.2, Page 18-11, Table 18-9   |  |  |

| 85.  | 272736-001           | 59   | Section 20.4, Page 20-11                 |  |  |

| 86.  | 272736-001           | 59   | Section 20.4, Page 20-17, Figure 20-12   |  |  |

| 87.  | 272736-001           | 60   | Section 20.4, Page 20-18, Figure 20-13   |  |  |

| 88.  | 272736-001           | 60   | Section 20.5.1, Page 20-19               |  |  |

| 89.  | 272736-001           | 60   | Section 20.5.2, Page 20-20               |  |  |

| 90.  | 272736-001           | 60   | Section 22.2, Page 22-1                  |  |  |

| 91.  | 272736-001           | 60   | Section 23.2.4.4, Page 23-9, Table 23-4  |  |  |

| 92.  | 272736-001           | 63   | Appendix A, Page A-4, Table A-5          |  |  |

272918-007 March, 1997 11 of 62

### **IDENTIFICATION INFORMATION**

# Markings

80960Rx processors may be identified electrically according to device type and stepping. Refer to the *i960*<sup>®</sup> *RP I/O Processor at 5 Volts* Data Sheet or the *i960*<sup>®</sup> *RP/RD I/O Processor at 3.3 Volts* Data Sheet for instructions on how to obtain the identifier number.

| Device and Stepping                      | Processor Device<br>ID Register<br>(PDIDR) (g0) | PCI-to-PCI Bridge Unit<br>Revision ID Register<br>(RIDR) (1008H) | Address Translation Unit<br>Revision ID Register<br>(ATURID) (1208H) |

|------------------------------------------|-------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------|

| 80960RP 33/5.0 A-0                       | 0x00860013                                      | 0x00                                                             | 0x00                                                                 |

| 80960RP 33/5.0 A-1                       | 0x10860013                                      | 0x01                                                             | 0x01                                                                 |

| 80960RP 33/3.3 A-0<br>80960RD 66/3.3 A-0 | 0x08861013                                      | 0x02                                                             | 0x02                                                                 |

#### FRRATA

### 1. Loss of local grant signal during an expansion ROM access

**PROBLEM:** This occurs when the memory controller wait state MMRs are set to their maximum number of wait states. On an primary PCI inbound access through the expansion ROM window, ATU REQ# is deasserted during an 80960 local bus recovery state. This causes GNT# to deassert and arbitration is granted to the i960 core processor, but the ATU is still mastering recovery cycles. Contention occurs on the bus, the i960 core processor hangs, and incorrect data is returned from the expansion ROM access.

**IMPLICATION:** Under the conditions outlined above, when the workaround is not used, this erratum could cause: internal bus contention, and erroneous data to be returned from the expansion ROM access.

**WORKAROUND:** Do not allow other masters (ATUs, DMAs) to access the 80960 local bus while reads to the expansion ROM window are occurring. In a typical system, expansion ROM accesses only occur during the initialization sequence, while DMAs and ATUs are typically inactive. In addition, program the memory controller programmable recovery states for ROM accesses (T<sub>WRR</sub>) to 0 or 1.

### 2. Byte enables, BE1:0#, can cause hold violations to flash memory

**PROBLEM:** When communicating with 8-bit memory, the Memory Controller Unit (MCU) provides address bits 13:2 on pins MA11:0, and address bits 1:0 on pins BE1:0#. The address is not held on the BE1:0# pins during recovery cycles. Some flash memories specify an address hold time relative to the deassertion of WE#. This is not a problem with the MA pins, but is a problem with the BE1:0# pins when they act as address signals.

**IMPLICATION:** Under the conditions outlined above, this erratum could cause problems with programming on-board flash devices if one of the workarounds is not used. This erratum only occurs during writes to flash memory. Read operations are not affected. In particular, the 80960Rx will not encounter any problems reading from a "pre-programmed" flash device.

# WORKAROUND: Adhere to the following:

- 1. Use flash devices that have a zero (0 ns) address hold time requirement.

- 2. Externally buffer BE1:0# to provide the necessary hold time.

3. The loss of HOLD on the 80960 local bus from an external bus master during a DRAM refresh cycle could cause bus ownership issues with the primary ATU, the Messaging Unit, or the expansion ROM

PROBLEM: The following events must happen for this erratum to occur:

- 1. A normal inbound read on the primary or secondary ATU must be occurring.

- 2. An MU read or an expansion ROM read is requesting the bus.

- 3. An external bus master requests the bus by asserting the HOLD pin.

- 4. A DRAM refresh occurs while the ATU is still the bus master. During the refresh, the HOLD pin is deasserted. After the refresh, both the ATU (to finish its read transaction) and the MU/expansion ROM interface simultaneously own the bus. This causes bus contention.

**IMPLICATION:** Under the conditions outlined above, this erratum could cause internal bus contention if the workaround is not used.

**WORKAROUND:** Do not allow an external bus master that is requesting the 80960 local bus to deassert the HOLD pin without first receiving HOLDA.

# 4. Unaligned DMA read transfers could prevent further operation of DMA Unit

**PROBLEM:** This problem occurs with unaligned DMA transfers that use memory read, memory read line, or memory read multiple PCI commands. During an unaligned DMA Read transfer, the DMA "builds" complete WORDs in its buffer from the unaligned data being read from the PCI bus. If the DMA unit loses control of the 80960 local bus after two consecutive local bus cycles AND there is only a partial WORD (1, 2 or 3 bytes) remaining in the DMA buffer to be written into 80960Rx local memory, that partial WORD is never transferred. The partial WORD remains in the DMA buffer and prevents further operation of the DMA channel.

Conditions or modes which increase the likelihood of losing control of the 80960 local bus on consecutive cycles include: demand mode DMA, DMA transfers that cross a 2 Kbyte boundary, having the Local Bus Arbitration Latency Counter Register (LBALCR) set to a low value.

**IMPLICATION:** Under the conditions outlined above, if one of the workarounds is not followed, the DMA channel could cease to function.

**WORKAROUND:** Either of two workarounds can prevent this erratum:

1. In demand mode, perform only aligned transfers.

2. In block transfer mode, make sure that unaligned DMA transfers do not cross and then end on a 2 Kbyte boundary with a partial word to transfer. This can be done by adding the destination address register and the byte count register and logically ANDing that result with 0x000007FF. If the final result is either 1, 2 or 3 bytes, then the DMA transfer should be broken up into two separate transfers where the final transfer moves the partial word. This can easily be accomplished using the DMA chaining mode on the 80960Rx. The LBALCR register should also be programmed to a value greater than 10.

### 5. Bridge Control Register can only be written as a 16-bit value

**PROBLEM:** The 80960Rx latches write data into the Bridge Control Register based on the state of lower byte enable only. The 80960Rx does not check the state of upper byte enable. This erratum applies to the Configuration Writes from the primary PCI interface as well as Local Bus writes from the i960 core processor.

**IMPLICATION:** A byte write to the lower byte of the Bridge Control Register causes data to be written to all 16 bits of the register, including the upper byte of the register (namely bits 8, 9 and 11). The data written to these bits is random. A byte write to the upper byte of the Bridge Control Register does not change the contents of the register.

**WORKAROUND:** Write the Bridge Control Register as a short word (16-bits).

# 6. Parity checking for inbound PCI address cycles is always enabled for the ATU

**PROBLEM:** The Parity Checking Enable bit (bit 06) in the primary and secondary ATU Command Registers (local bus address 1204H and 1298H) only affects inbound parity checking on PCI data cycles. Parity checking is always enabled for address cycles regardless of this bit's setting.

**IMPLICATION:** PCI masters that access 80960Rx local memory through the ATUs must generate address parity.

**WORKAROUND:** Make certain to connect the P\_PAR and S\_PAR signals from the 80960Rx to their respective PCI buses. Use PCI masters that generate address parity in all cases.

# 7. Configuration Write Cycle occurring simultaneously with clearing the Configuration Cycle Retry bit causes a deadlock problem

**PROBLEM:** In initialization modes 1 and 3, all PCI configuration cycles targeted at the 80960Rx on the primary PCI bus are retried until the Configuration Cycle Retry bit in the Extended Bridge Control Register (local bus address 1040H) is cleared by 80960Rx software. This allows software to setup the 80960Rx registers before the system host BIOS can configure it. The 80960Rx may enter a lockup condition which can only be cleared by a RESET when:

- the first configuration cycle to the 80960Rx is a write cycle which is being retried, and

- the Configuration Cycle Retry bit is cleared

The configuration cycle must be a write; configuration reads function properly when the Configuration Cycle Retry bit is cleared.

**IMPLICATION:** When used in applications where the first configuration cycle targeted at the 80960Rx is a write cycle, the 80960Rx may enter a lockup that can only be cleared by a device RESET. For PCI add-in card or motherboard applications, the system BIOS generates the initial configuration cycles.

**WORKAROUND:** For applications where the first configuration cycle targeted at the 80960Rx could be a write cycle, use initialization modes 0 or 2.

# 8. PCI Master Parity Error bits set in Bridge Interrupt Status Registers regardless of whether parity checking is enabled

**PROBLEM:** The PCI Master Parity Error bits (Bit 0) in both the Primary and Secondary Interrupt Status Registers (local bus addresses 1044H and 1048H) are set when a parity error occurs regardless of whether or not parity checking has actually been enabled. Parity checking is enabled and disabled for the primary side by bit 6 of the Primary Command Register (local bus address 1004H) and for the secondary side by bit 0 of the Bridge Control Register (local bus address 1040H).

**IMPLICATION:** An NMI# to the i960 core processor is generated when either of the PCI master Parity Error bits are set.

**WORKAROUND:** The user's NMI# interrupt service routine should ignore NMI#s generated by PCI Master Parity Errors when parity checking has been disabled.

# 9. Deadlock condition under simultaneous inbound read and outbound write PCI traffic through secondary ATU

**PROBLEM:** A single 64-byte data queue in the secondary ATU is shared between inbound reads and outbound writes. This failure mode occurs when three conditions exist around the same internal clock edge:

- 1. A PCI master is reading data from the last location of the 64-byte data queue.

- 2. That same location is being filled from the 80960 local bus.

- 3. An outbound write occurs from the i960 core processor.

The internal queue control logic can potentially deadlock on these three conditions. The inbound read completes correctly but the outbound write never occurs. The 64-byte inbound read/outbound write queue is deadlocked and will accept no further transfers from either the secondary PCI bus or the 80960 local bus.

This failure mode only occurs on the secondary ATU; the primary ATU is not affected.

**IMPLICATION:** During heavy inbound read and outbound write traffic, the shared 64-byte inbound read/outbound write queue can deadlock. This condition can only be cleared by a device reset.

#### WORKAROUND: Three workarounds are:

- 1. Limit inbound PCI reads through the secondary ATU to 60 bytes or less.

- Use the DMA controller to transfer data between the secondary PCI bus and the 80960Rx's local memory.

- 3. Don't perform simultaneous inbound reads and outbound writes through the secondary ATU.

# 10. Intermittent ONCE Mode upon power-up

**PROBLEM:** Intermittently, the device may enter ONCE Mode when excessive noise is present on the system's P\_RST# signals. When in ONCE Mode the internal PLLs are stopped and all output signals are floated.

**IMPLICATION:** In some systems the power ramp and noise on the P\_RST# signal may cause the device to enter ONCE Mode. This condition can only be cleared by device reset (cycling power off and on).

**WORKAROUND:** Ensure that the P\_RST# signal is "noise-free" during the power ramp. ONCE Mode may be entered on through the JTAG port using the HIZ instruction. The ability to enter the ONCE mode by asserting the LOCK#/ONCE# pin during reset is disabled in the 80960RP 33/5.0 A-1 stepping.

# 11. ATU lockup condition under simultaneous outbound read data and inbound write data through the inbound data queue

**PROBLEM:** In each ATU, a 64-byte inbound data queue is shared by both outbound reads and inbound writes. A boundary condition causes an ATU deadlock when an outbound read from the i960 core processor begins during a bus master-initiated (IRDY# asserted) inbound write transaction. For this condition to occur, the inbound write's first address-to-data cycle must have more than three master inserted (IRDY#) wait states. Subsequent address-to-data cycles are not affected during the inbound write transaction. This problem can occur in either the primary or secondary ATU.

**IMPLICATION:** Under heavy use, the ATU deadlocks when using PCI masters that initiate inbound writes with greater than three master inserted (IRDY#) wait states. This condition can only be cleared by a device reset.

WORKAROUND: Three possible workarounds are:

- 1. Use bus masters that do not initiate writes through the inbound data queue that use greater than three master inserted (IRDY#) wait states.

- 2. Use the DMA channel to transfer data from the PCI bus to the 80960 local bus.

- Do not perform simultaneous outbound reads and inbound writes through the ATUs.

# 12. PCI-to-PCI bridge can corrupt data during Memory Write and Invalidate cycles that insert IRDY# wait states during data-data transfers

**PROBLEM:** The 80960RP 33/5.0's integrated PCI-to-PCI bridge has 16 dword upstream and downstream posted write queues. The bridge corrupts data in the posted write queues when a PCI master writing into the queues inserts one or more IRDY# wait states in between the 15th and 16th dword during MWI cycles. This problem only affects MWI cycles; memory write cycles function correctly.

**IMPLICATION:** The PCI-to-PCI bridge corrupts data when used with PCI masters that insert IRDY# wait states during MWI cycles.

#### WORKAROUND: Two workarounds are:

- Program the PCI-to-PCI bridge cacheline size register (Local bus offset 0x100CH) to 0. This aliases all MWI commands and memory write commands. This workaround can limit write performance when used with host bridges that are optimized for MWI commands.

- 2. Do not use PCI masters that insert IRDY# wait states during MWI commands.

# 13. Using the Messaging Unit circular queues with more than one recovery wait state on the local bus can cause primary Address Translation Unit data corruption

**PROBLEM:** When using the Messaging Unit (MU) circular queues with more than one recovery wait state on the 80960 local bus, data corruption in the primary ATU occurs. Specifically, inbound reads through the primary ATU return incorrect data, and inbound writes never propagate to 80960RP 33/5.0 local memory. This errata only affects the circular queue functionality of the MU: no other messaging unit functionality (i.e., doorbell registers, index registers, etc.) is affected.

**IMPLICATION:** Data corruption can occur when using the circular queues and the primary ATU when more than one recovery wait state is inserted during 80960 local bus cycles.

**WORKAROUND:** Never insert more than one additional recovery wait state during any 80960 local bus cycle when using the circular queues and the primary ATU. Note that the 80960RP 33/5.0 explicitly inserts one recovery cycle into every 80960 local bus access. This workaround is for additional recovery states. For designs that use the on-chip memory controller, this can be done by programming the proper device registers. The following bit locations in these registers affect recovery cycles and must be programmed to a 0 or 1:

- Memory Bank Read Wait States Register bits 2:0 (MBRWS1:0 at offset 1508H, 1514H)

- Memory Bank Write Wait States Register bits 2:0 (MBWWS1:0 at offset 150CH, 1518H)

- DRAM Bank Read Wait State Register bits 1:0 (DRWS at offset 1524H)

- DRAM Bank Write Wait State Register bits 1:0 (DWWS at offset 1528H)

When programming the Memory Controller for interleaved FPM DRAM, the number of write cycle CAS# delays ( $T_{WCP}$ ) adds to the number of recovery states. For example, in a typical interleaved FPM design,  $T_{WCP}$  is programmed for 1.5 cycles (bits 9:8 in the DWWS register set to 00 or 01). One additional write recovery wait state is also inserted. In this case, the write recovery wait states must be cleared to 0 (bits 1:0 in the DWWS register cleared to 00) for this errata. When programmed for zero additional recovery cycles, the memory controller de-asserts RAS# for two clock cycles to satisfy the RAS# pre-charge specification of the DRAM.

# 14. Access to non-existent DRAM causes incorrect error reporting

**PROBLEM:** An 80960 local bus fault error occurs when the i960 core processor attempts to access an invalid local bus memory address and the Bus Monitor Interrupt (BMER register at local bus address 1534H) is enabled. The next valid inbound ATU access occurring after the local bus fault causes a target abort on the PCI bus. The errors reported in the Primary ATU Interrupt Status Register are: 80960 Bus Fault and PCI Target Abort (target).

**IMPLICATION:** A valid inbound ATU transaction incorrectly generates a PCI target abort when a bus monitor interrupt occurs.

**WORKAROUND:** Do not enable the Bus Monitor Interrupt feature. To disable this feature, clear bit 0 of the Bus Monitor Enable register, which is located at local bus offset 1534H.

# 15. Address Translation Unit write and Messaging Unit queue port write may get out of order on the 80960 local bus

**PROBLEM:** An inbound ATU data write and an inbound MU queue port write can get out of order on the 80960 local bus. The MU queue port write may complete before the ATU data write completes on the local bus, regardless of whether the MU queue port write began after the ATU data write on the PCI bus.

An interrupt is generated to the i960 core processor when the write to the MU queue port occurs. Because the ATU write could still be pending in the 80960Rx inbound write buffer, the interrupt service routine could potentially read bad data from local memory if it depended on the ATU write completing before the MU queue port write.

**IMPLICATION:** Invalid data could be read from the 80960Rx local memory if a user application depended on the 80960Rx maintaining order between ATU and messaging unit writes.

**WORKAROUND:** To prevent the i960 core processor from reading the message data, before the ATU completes the write, program the Local Bus Arbitration Latency Counter Register (LBALCR) to a value large enough to prevent the core processor from accessing the Local Bus between the two transactions. The value needed in the LBALCR must handle both the Message Unit transaction, the ATU transaction, and a potential DRAM refresh cycle. Use the following equation to calculate the minimum LBALCR value:

where:

TRC is the number of wait states between address and the first data.

TRC = TRRC + 2 (T<sub>RRC</sub> is the DRAM read cycle RAS-to-CAS delay), or

# int<sub>el®</sub>

#### 80960Rx SPECIFICATION UPDATE

$T_{RC} = T_{WRC} + 2$  ( $T_{WRC}$  is the DRAM write cycle RAS-to-CAS delay)

T<sub>CP</sub> is the number of wait states between data during a burst.

$T_{CP} = T_{RCP}$  ( $T_{RCP}$  is the DRAM read cycle CAS pulse width), or

$T_{CP} = T_{WCP}$  ( $T_{WCP}$  is the DRAM write cycle CAS pulse width)

T<sub>RCV</sub> is the number of recovery cycles at the end of a DRAM access.

T<sub>RCV</sub> = T<sub>RRCV</sub> + 1 (T<sub>RRCV</sub> is the DRAM read cycle additional recovery wait states), or

$T_{RCV} = T_{WRCV} + 1$  ( $T_{WRCV}$  is the DRAM write cycle additional recovery wait states)

These values are found in the DRAM Bank Read Wait State (DRWS) and DRAM Bank Write Wait State (DWWS) registers. The 26 cycles includes 20 cycles for a worst case DRAM refresh cycle.

#### For example:

$T_{RRC} = T_{WRC} = 1$ ;  $T_{RC} = 3$  (3 wait states from address to data)

$T_{RCP} = T_{WCP} = 0$ ;  $T_{CP} = 0$  (0 wait states between data)

$T_{RRCV} = T_{WRCV} = 1$ ;  $T_{RCV} = 1$  (1 extra recovery cycle after DRAM access)

Then,

LBALCR = 26 + (2 \* 3) + (16 \* (1 + 0)) + (2 \* 1) = 50 = 32H

# 16. Using multiple DMA channels that perform unaligned transfers can cause a DMA channel performing a read to stop operating

**PROBLEM:** When using two or more DMA channels simultaneously — one DMA channel is performing a read operation, and at least one of the other DMA channels is unaligned — the DMA channel performing a read may terminate its task. Aligned means the source address and destination address are both on the same byte boundary.

**IMPLICATION:** The DMA channel performing the read terminates and is no longer operational.

WORKAROUND: You may use any of the following workarounds:

- 1. Use only one DMA channel at a time.

- 2. Operate all DMA channels aligned.

- If the DMA channels are only performing writes, the channels can be aligned or unaligned.

- 4. If multiple DMA channels are used, one read channel can be aligned or unaligned if the other channel(s) is(are) performing aligned writes.

# 17. Messaging Unit logs multiple interrupt sources when using the index registers

**PROBLEM:** Accesses to an index register within the Messaging Unit (MU) cause multiple interrupt status bits to be set in the Inbound Interrupt Status Register (IISR). The bits are the Index Register Interrupt (bit 06), Inbound Doorbell Interrupt (bit 02), Inbound Message 1 Interrupt (bit 01), and Inbound Message 0 Interrupt (bit 00). This occurs when the Inbound Interrupt Mask Register's Index Register Interrupt Mask bit is set or cleared.

**IMPLICATION:** 80960RP software cannot correctly determine the source of the interrupt in the MU when the Index Registers are used with another function in the MU.

WORKAROUND: Do not use the index registers with either:

- Doorbell registers and Message Queues

- Message registers and Message Queues

### 18. DMA Descriptors appended to the end of a chain may not execute

**PROBLEM:** A descriptor appended to a DMA chain may not execute when the Chain Resume bit (bit 01) is set in the Channel Control Register. This occurs when:

- 1. The last descriptor of the existing chain is a DMA read, and

- 2. The Chain Resume bit is set when the last word of the DMA is being transferred.

When condition 1 and 2 occur, the DMA unit does not re-read the Next Descriptor Address (NDA) of the current descriptor.

This erratum exists for both aligned and unaligned DMA transfers.

**IMPLICATION:** A DMA transfer from an appended DMA descriptor may not execute.

WORKAROUND: Two workarounds can be used to prevent this errata:

- 1. Add a NULL descriptor to the end of a chain where the last descriptor is a read. This applies to original chains and to appended chains even when the appended chain is one descriptor in length. The NULL descriptor has a Byte Count = 0000H, and an NDA of 0000H. A NULL descriptor at the end of a DMA chain is appended in the normal manner the NDA of the last descriptor of the existing chain is changed to point to the new chain then the Chain Resume bit is set.

- Append chains as normal, then poll the state of the Channel Active Flag (bit 10) in the Channel Status Register. When the flag is cleared, set the Chain Resume bit once more.

# 19. Downstream exclusive read transaction through multiple bridges may cause a deadlock condition

**PROBLEM:** A deadlock condition is possible with an 80960Rx behind another 80960Rx during a downstream exclusive read transaction. The condition occurs when the upstream bridge attempts the exclusive access on its secondary PCI bus and the downstream bridge has a posted memory write (PMW) transaction in its queue. The ordering rules require the downstream bridge to complete the upstream PMW before accepting the downstream read transaction. The upstream bridge, however, retries all upstream transactions once it begins the exclusive downstream transaction, and retries the downstream bridge's PMW, thus causing a deadlock condition.

**IMPLICATION:** Under the conditions outlined above, the 80960Rx bridge unit may deadlock.

**WORKAROUND:** To prevent this erratum do not perform locked PCI transactions to PCI devices downstream of the 80960Rx.

### 20. Inbound ATU PCI read issue with retried completion cycles

**PROBLEM:** For inbound ATU read requests, both primary and secondary ATUs implement delayed transactions per the *PCI Local Bus Specification*, revision 2.1. When a PCI initiator attempts to read from an inbound ATU, the initial request is retried while the ATU begins reading the data from the 80960 local bus. Once the data is in the inbound read queue, the initiator completes the transaction during the delayed completion cycle. The ATU can deadlock when a second initiator attempts to read the same address location with a different transfer length before the first master returns from its retry cycle.

**IMPLICATION:** When two PCI initiators are accessing the same address location with different length data requests, the ATU can potentially deadlock. The ATU only recovers from this condition with a device RESET (P\_RST#).

**WORKAROUND:** Ensure that your 80960Rx application does not allow two PCI masters accessing the same memory address location simultaneously through either the primary or secondary ATU.

# 21. Null writes (BE3:0# deasserted) to the MU Inbound and Outbound Queue Ports corrupt the corresponding queue pointer

**PROBLEM:** A *null write* is defined as a write cycle on the PCI bus when all Byte Enables are deasserted; no data is actually transferred. When a null write occurs to either the Inbound or Outbound Queue port, the queue pointers are incremented. These queue ports are part of the Messaging Unit and are located at offset 0040H and 0044H in the first 4 Kbytes of the Primary Inbound ATU PCI Address Space.

**IMPLICATION:** The queue pointers are corrupted when a host bridge or another PCI device performs a null write to either the Inbound or the Outbound Queue ports.

**WORKAROUND:** Always perform only 32-bit DWORD writes to the both the Inbound Queue Port and the Outbound Queue Port in the Messaging Unit.

# 22. PCI-to-PCI Bridge Unit can corrupt data during Memory Write cycles when wait states are inserted simultaneously on both the primary and secondary sides of the bridge

**PROBLEM:** The 80960RP's integrated PCI-to-PCI bridge has 16-DWORD upstream and downstream posted write queues. The bridge can corrupt data in the posted write queues when a PCI initiator writing into the queues inserts IRDY# wait states between the 15th and 16th DWORD at the same time that the target inserts TRDY# wait states on the other side of the bridge during Memory Write cycles.

**IMPLICATION:** The PCI-to-PCI bridge corrupts data when used with PCI initiators and corresponding targets that insert wait states during memory write cycles.

**WORKAROUND:** Either of two workarounds can prevent this erratum:

- Do not use PCI masters that insert IRDY# wait states during Memory Write commands.

- Disable write posting: clear bit 00 of the Extended Bridge Control Register (EBCR), local bus address 1040H.

#### SPECIFICATION CHANGES

### 1. PCI Interrupt Routing Select Register (PIRSR) Polarity

**ITEM:** The polarity of the XINT Select bit (bit 0) in the PCI Interrupt Routing Select Register (PIRSR) has changed. Previous to the 80960RP 33/5.0 A-0 stepping, it was specified as:

- 0 Interrupts routed to i960 core processor interrupt controller input. This is the default condition when the 80960RP 33/5.0 is reset.

- 1 Interrupts routed to P INTX# pins.

In the 80960RP 33/5.0 A-0 stepping, the specification is changed to:

- 0 Interrupts routed to P\_INTX# pins. This is the default condition when the 80960RP 33/5.0 is reset.

- 1 Interrupts routed to i960 core processor interrupt controller input.

This allows the 80960RP 33/5.0 to function as a stand-alone bridge while the core is held in reset as in Initialization Mode 0.

#### 2. Asynchronous clocking mode not supported

**ITEM:** The *i960*<sup>®</sup> *RP Microprocessor User's Manual* (272736-001) describes an asynchronous clocking mode which allows the secondary PCI bus and the i960 core processor to run at an asynchronous and slower frequency than the primary PCI bus. This mode of operation is not supported. Synchronous mode is the only clocking mode specified.

For proper operation, the WIDTH/HLTD0/SYNC pin should either remain unconnected or pulled high with a 10 K ohm pullup resistor. The P\_CLK pin should be tied to V<sub>CC</sub> or V<sub>SS</sub>.

# 3. The MU interlock mechanism remains enabled for APIC registers when the APIC is disabled

**ITEM:** On the first access by a PCI master to the APIC registers in the Messaging Unit, the interlock mechanism is expected to generate an interrupt to the i960 core processor. If the PCI master returns and writes to an APIC register, the MU will retry the master until the interrupt is cleared. If the APIC is disabled, the interrupt is never generated, and thus never cleared, causing a PCI master lockup condition.

Do not access the two APIC registers in the MU unless the APIC Unit is enabled. These registers are: APIC Register Select Register (ARSR) and APIC Window Register (AWR).

### 4. Incorrect BIOS access of block size from Base Address Registers

**ITEM:** To determine the block size requirements of a PCI device, the system BIOS is to write all ones (FFFF FFFFH) to the base address register then read back the register. The returned value indicates the block size requirements based on which bits are set to one (i.e., the memory required for the PCI device). When performing this operation, some system BIOS' write FFFF FFFEH to the base address register.

To determine the proper block size requirement, a value of FFFF FFFFH is written to the base address register. The next read after the FFFF FFFFH write is then directed to the limit register instead of the base register; the limit register is then used to determine the block size required.

The specification is changed to define that either of the following values can be used to determine the block size for the device:

- all ones (FFFF FFFFH)

- all ones except bit 0 (FFFF FFFEH)

This affects the Primary Inbound ATU Base Address Register, the Expansion ROM Base Address Register, and the Secondary Inbound ATU Base Address Register.

See also Documentation Change for Section 16.7.14.1, Page 16-38.

## 5. ATU Configuration Register Bit 12 Definition is Changed

**ITEM:** The ATU Configuration Register (ATUCR) Bit 12 was previously defined as "Reserved"; it is now defined as "Secondary Bus, Messaging Unit Access Enable". See definition below; see also the Documentation Change for Section 16.7.32, Page 16-51, Table 16-43.

| Bit | Default | R/W        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | 02      | Read/Write | Secondary Bus, Messaging Unit Access Enable - When set, the PCI-to-PCI Bridge unit can forward a transaction from the secondary PCI interface, through the bridge, and to the Messaging Unit (first 4 Kbytes of the PATU inbound address space) on the primary PCI interface. For correct operation, the transaction must be a valid bridge address (claimed by secondary interface of the bridge and forwarded to the primary interface of the bridge) as well as a valid Messaging Unit address. When clear, the Messaging Unit cannot claim a transaction mastered by the primary interface of the bridge. |

6. Multiple reads of the Base Address Register after writing all 1's will return different values (See Specification Clarification Item #5)

(In previous revisions of this document, this item was redundant with a Specification Clarification.)

7. Additional devices can be configured as public or private on the secondary PCI bus by programming the Secondary IDSEL Select Register (SISR)

**ITEM:** Bits 5 through 9 of the Secondary IDSEL Select Register (SISR) now can be used to mask the SAD21 through SAD25 during type 1 to type 0 configuration cycles on the secondary bus. This enables up to 10 devices to be configured as public or private devices on the secondary PCI bus.

8. PCI Interrupt Routing Select Register (PIRSR) now supports individual routing of each XINT3:0# pin

**ITEM:** Bits 3:0 of the PCI Interrupt Routing Select Register (PIRSR) individually control the routing of the XINT3:0# pins to either the i960 core processor or the corresponding P INTx# pin:

- Setting a bit to a 1 routes the corresponding interrupt to the i960 core processor.

- Clearing the bit to a 0 routes the corresponding interrupt to the P\_INTx# pin.

- 9. The Memory Bank Extended MWE3:0# bits in the Memory Bank Control Register can provide one clock of address hold time during write cycles

**ITEM:** The description for both Memory Bank 1 Extended MWE3:0# bit and Memory Bank 0 Extended MWE3:0# bit should now read:

"This bit field enables or disables extending the deassertion period for the MWE3:0# signal during burst write cycles. The bit also enables one clock of MA11:0 and BE1:0 hold time relative to the rising edge of MWE# during writes to this region.

- When cleared (0), deassertion period is one-half of a CLKIN period.

- When set (1), the deassertion period is extended by the wait state profile defined in the MBWWSx registers in addition to the one-half clock in period. Also when set, the MA11:0 and BE1:0 keep their current state for one clock after MWE3:0# are deasserted. This also adds an extra wait state."

# 10. Mask bits added for all PCI-PCI bridge error conditions which may cause an NMI# to the i960 core processor

**ITEM:** Bits 15 through 4 of the Secondary Decode Enable Register (SDER) now can be used to mask sources of NMI# from the bridge. When set to 1, the source of NMI# is masked. When cleared to 0, the source of NMI is enabled. See the following table:

Table 10-1. Secondary Decode Enable Register - SDER

PCI Configuration Address Offset: 5CH 80960 Core Local Bus Address: 105CH 12 R/W Bit Default Description 15 R/W Secondary SERR# Detected (Bit 4 of SBISR) 02 14 R/W Secondary PCI Master Abort (Bit 3 of SBISR) 02 R/W Secondary PCI Target Abort (Initiator, Bit 2 of SBISR) 13 02 12 02 R/W Secondary PCI Target Abort (Target, Bit 1 of SBISR) 11 R/W Secondary PCI Master Parity Error (Bit 0 of SBISR) 0, 10 02 R/W Primary SERR# Asserted or Detected (Bit 4 of PBISR) 09 R/W Primary PCI Master Abort (Bit 3 of PBISR) 02 08 R/W Primary PCI Target Abort (Initiator, Bit 2 of PBISR) 02 07 R/W Primary PCI Target Abort (Target, Bit 1 of PBISR) 02 R/W 06 Primary PCI Master Parity Error (Bit 8 of PSR) 02 05:03 Read Reserved  $000_{2}$ Only Private Memory Space Enable - when set, this bit disables Bridge Read/ forwarding of addresses in the SMBR/SMLR address range. This creates a 02  $0_2$ Write private memory space on the secondary PCI bus for peer to peer transac-Secondary Positive Memory Decode Enable - when set, this bit enables the secondary interface of the bridge unit to positively decode memory Read/ 01 02 addresses on the secondary bus. Addresses within the SMBR/SMLR Write address range is forwarded through the bridge. Inverse decoding is disabled. Secondary Positive I/O Decode Enable - when set, this bit enables the Read/ secondary interface of the bridge unit to positively decode I/O addresses on 00  $0_2$ Write the secondary bus. Addresses within the SIOBR/SIOLR address pair is forwarded through the bridge. Inverse decoding is disabled.

# 11. Multiple reads of the Base Address Register, after writing all 1's, returns the limit register value until rewritten

**ITEM:** The 80960Rx provides a programmable mechanism for defining the memory address block size requirements. This mechanism uses the Base Address Register (BAR) and corresponding limit register. 80960Rx initialization code programs into the limit register the desired value to be returned for memory block size. To determine the memory block size requirements, write FFFF FFFFH or FFFF FFFEH to the BAR, then read back the BAR value. Subsequent reads of the BAR returns the memory block size (i.e., it returns the limit register value until the BAR is rewritten with a value other than FFFF FFFH or FFFF FFFEH).

272918-007 March, 1997 29 of 62

#### SPECIFICATION CLARIFICATIONS

### 1. Five IDSEL lines for the secondary PCI bus are not enabled

**ITEM:** Bits 5 through 9 in the Secondary IDSEL Select Register (SISR); see page 15-58 of the *i960<sup>®</sup> RP Microprocessor User's Manual* (272736-001), may be used in future versions to enable the masking of S\_AD21:25 during Type 1 to Type 0 configuration cycles on the secondary PCI bus. These five signals (in addition to S\_AD16:20) will enable additional devices as public or private PCI devices in an intelligent I/O system.

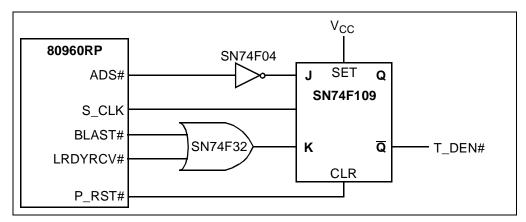

## 2. How to use the Data Enable (DEN#) Signal with an In-Circuit Emulator

**ITEM:** When using an ICE in your 80960Rx system, the use of the Data Enable signal (DEN#) is not recommended. This clarification describes how DEN# operates and a recommended solution for using it with an In-Circuit Emulator (ICE).