# Intelligent RAID Module

$I_2O$

PCI Spring Developers' Conference and Expo

K. K. Rao and Dawn Tse Mylex Corporation (510) 796-6100

#### **RAID Module**

- Hardware Architecture IOP platform

- Independent of microprocessor, bus, or controller type

- Firmware I<sub>2</sub>O compliant ISM (DDM)

## **Benefits of Design Approach**

- Efficient use of system resources

- Hierarchical RAID is easily configured

- Controls physical devices through HDMs

- Capacities no longer limited by bus configuration

- Fail-over to protect cache data is easily implemented

- Loadable to any I<sub>2</sub>O compliant IOPs

- Shortens time to market

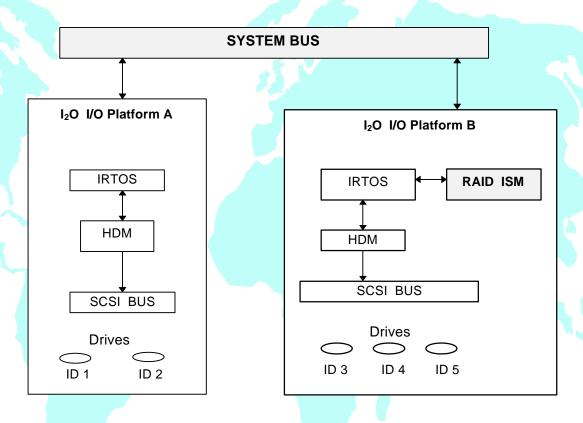

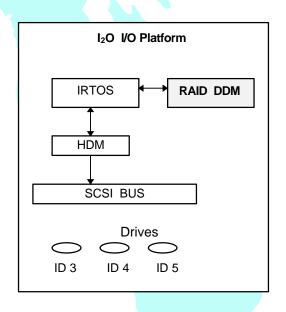

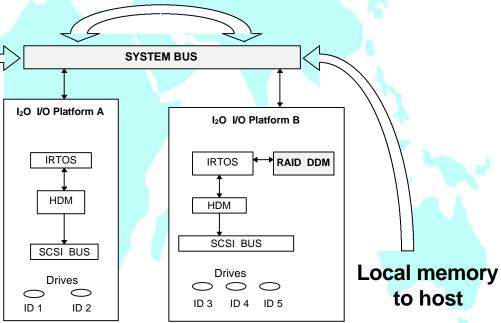

### **Operating Environment**

- IOP microprocessor, memory and IO devices

- RAID ISM high-performance and fault-tolerance

- RTOS provides APIs

- HDM controls physical devices

- Coexists with other I<sub>2</sub>O compliant DDMs or ISMs

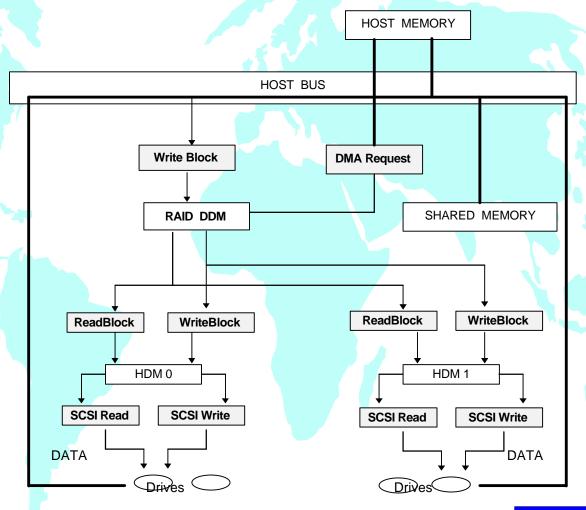

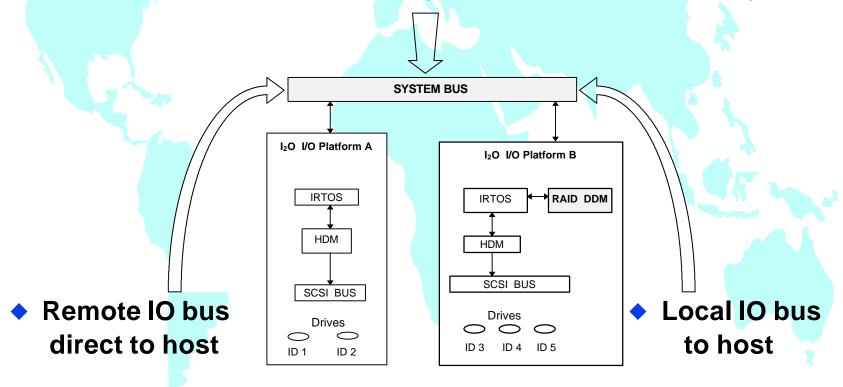

#### **RAID Data Path**

- Between shared memory and host memory or

- Removed shared memory and local shared memory

### **RAID Memory Modes**

- System Memory

- Accessible only from system bus

# IOP private memory Accessible only by local IOP Peer-to-peer memory transfer SYSTEM BUS

- Shared Memory

- Accessible by system bus,other IOPs

Remote memory shared to host

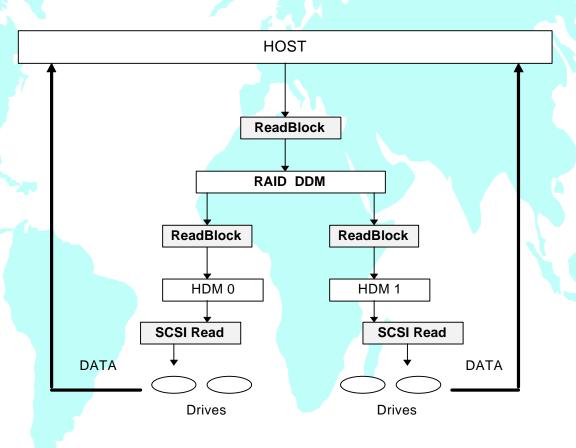

## **RAID** Read Operation

## **RAID Write Operation**