# AP-726 APPLICATION NOTE

# Interfacing the i960® Jx Microprocessor to the NEC µPD98401\* Local ATM Segmentation and Reassembly (SAR) Chip

**Rick Harris**

SPG 80960 Applications Engineer

Intel Corporation Semiconductor Products Group Mail Stop CH6-311 5000 W. Chandler Blvd. Chandler, Arizona 85226

September, 21, 1995

Order Number: 272779-001

# AP-726 APPLICATION NOTE

# Interfacing the i960® Jx Microprocessor to the NEC µPD98401\* Local ATM Segmentation and Reassembly (SAR) Chip

**Rick Harris**

SPG 80960 Applications Engineer

Intel Corporation Semiconductor Products Group Mail Stop CH6-311 5000 W. Chandler Blvd. Chandler, Arizona 85226

September, 21, 1995

Order Number: 272779-001

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

© INTEL CORPORATION 1995

#### AP-726

| 1.0 II       | NTRO                      | DUCTION                           | .1 |

|--------------|---------------------------|-----------------------------------|----|

| 1.1          | De                        | sign Goals                        | 1  |

| 1.2          | Ov                        | rerview                           | 1  |

| 1.3          | Pa                        | ge Mode DRAM SIMM                 | 2  |

| 1.4          | DF                        | RAM Refresh                       | 2  |

| 1.5          | Bu                        | rst Capabilities for a 32-bit Bus | 2  |

| 1.6          | Ва                        | nk Interleaving                   | 2  |

| 1.7          |                           | 60 Jx Processor Address Mapping   |    |

| 2.0 C        | IRCII                     | IIT DESCRIPTION                   | 3  |

| 2.1          |                           | ock Generation                    |    |

| 2.2          |                           | stem Address Latches              |    |

| 2.2          | •                         | RAM Controller                    |    |

| د.ی<br>2.3.1 |                           | Control Logic                     |    |

| 2.3.1        |                           | Address Flow Logic                |    |

| 2.3.2        |                           | Data Flow Logic                   |    |

| 2.3.4        |                           | State Machines and Signals        |    |

| 2.3.4        |                           | DRAM Control State Machine        |    |

| _            | .4.1<br>.4.2              | SELDRAM Signal                    |    |

| _            | .4.2<br>.4.3              | REFPEND Signal                    |    |

| _            | .4.3<br>.4.4              | MEMPEND Signal                    |    |

| _            | .4. <del>4</del><br>.4.5  | MUX Signal                        |    |

| _            | . <del>4</del> .5<br>.4.6 | CASEN Signal                      |    |

|              | . <del>4</del> .0<br>.4.7 | INCBANK and BANKSEL Signals       |    |

|              | .4.8                      | CASA[3:0] and CASB[3:0] Signals   |    |

| _            | .4.9                      | MA0B and MA0A Signals             |    |

| _            | .4.10                     | RDYEN Signal                      |    |

| _            | .4.11                     | READY Signal                      |    |

|              | .4.12                     | DWE Signal                        |    |

| 2.4          |                           | NR slave controller               |    |

| <br>2.4.1    |                           | Control Logic                     |    |

| 2.4.2        | )                         | Address Flow Logic                |    |

| 2.4.3        |                           | Data Flow Logic                   |    |

| 2.4.4        |                           | State Machine and Signals         |    |

| 2.4          | .4.1                      | SELC Signal                       |    |

| 2.4          | .4.2                      | SELSQ0 Signal                     |    |

| 2.4          | .4.3                      | SAR Access State Machine          | 11 |

| 2.4          | .4.4                      | READYn Signal                     | 11 |

| 2.4          | .4.5                      | READYpinn Signal                  |    |

| 2.4          | .4.6                      | RDYENn Signal                     | 11 |

| 2.4          | .4.7                      | SARSELn Signal                    | 11 |

| 2.4          | .4.8                      | SARASELn Signal                   | 11 |

# intel

#### AP-726

| 2   | .4.9 SARSWRn Signal               | 11 |

|-----|-----------------------------------|----|

| 2   | .4.10 AOEABn Signal               | 11 |

| 2   | .4.11 DOEABn Signal               | 11 |

| 2   | .4.12 DOEBAn Signal               | 12 |

| 3.0 | DRAM CONTROLLER ACCESS FLOW       | 12 |

| 3.1 | Single Word Read and Write Access | 12 |

| 3.2 | Quad Word Read Access             | 14 |

| 3.3 | Quad Word Write Access            |    |

| 3.4 | CAS before RAS Refresh            | 17 |

| 4.0 | SAR SLAVE ACCESS FLOW             |    |

| 4.1 | Single Word Read and Write Access | 17 |

| 5.0 | CONCLUSION                        | 20 |

| 6.0 | RELATED INFORMATION               | 20 |

| ΔΡΕ | NDIX A                            |    |

APPENDIX A

PLDshell FILES

APPENDIX B

PLD EQUATIONS

INDEX

#### AP-726

| <b>FIGURES</b> |                                                                           |

|----------------|---------------------------------------------------------------------------|

| Figure 1.      | Quad-Word Write Request with 2,1,1,1 Wait State Profile                   |

| Figure 2.      | Two-Way Interleaving                                                      |

| Figure 3.      | 80960Jx Interface Memory Map                                              |

| Figure 4.      | i960®Jx Processor to DRAM / NEC μPD98401 SAR Bus Interface                |

| Figure 5.      | System Address Latches                                                    |

| Figure 6.      | DRAM Address Flow Logic                                                   |

| Figure 7.      | DRAM Control State Machine                                                |

| Figure 8.      | Simplified DRAM State Machine                                             |

| Figure 9.      | SAR Address and Data Buffers                                              |

| Figure 10.     | 80960Jx to SAR Access State Machine                                       |

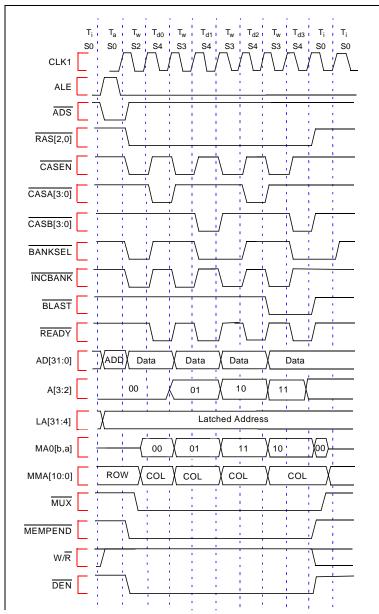

| Figure 11.     | 80960Jx to DRAM 1 Wait State Single Word Read and Write Timing Diagram 13 |

| Figure 12.     | 80960Jx to DRAM 1,0,0,0 Quad Word Read Timing                             |

| Figure 13.     | 80960Jx to DRAM 1,1,1,1 Quad Word Write Timing Diagram 16                 |

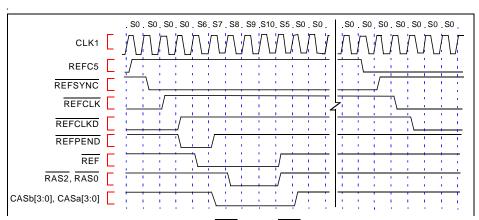

| Figure 14.     | CAS-Before-RAS Refresh Cycle                                              |

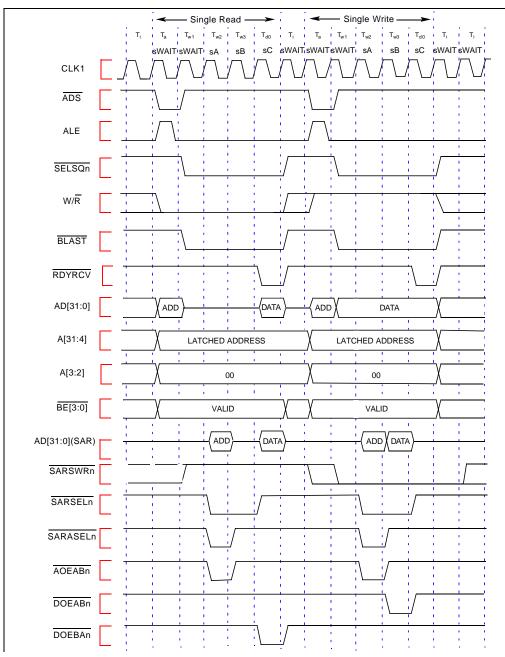

| Figure 15.     | 80960Jx to μPD98401 Single Word Read and Write Timing Diagram             |

| TABLES         |                                                                           |

| Table 1.       | Related Information                                                       |

| Table A-1.     | DRAM Controller EPX780 PLDshell File                                      |

| Table A-2.     | DRAM Controller PAL20V8 PLDshell.File                                     |

| Table B-1.     | SAR Controller MACH210, MACHXL File 1                                     |

#### 1.0 INTRODUCTION

This application note describes the interface between Intel's i960  $^{\rm @}$  JA/JF/JD microprocessors (referred to herein as the "i960 Jx processor") and NEC's  $\mu PD98401^{\rm @}$  Local ATM Segmentation And Reassembly (SAR) Chip, with 2 Mbytes of DRAM available to the i960 Jx processor. The interface provides for single and burst reads/writes to the DRAM and single reads and writes to the SAR chip, using the i960 Jx processor configured with a 32-bit bus. The interface is controlled by a DRAM controller and a SAR controller.

The DRAM interface features include:

- 32 bit wide bus, allowing 16 and 8 bit accesses

- · Two-way interleaving

- 72 pin, 60 ns, 256 Kbyte x 32 bit Fast Page Mode DRAM SIMMs

- 1-0-0-0 wait state burst reads at 25 MHz

- 1-1-1-1 wait state burst writes at 25 MHz

The µPD98401 SAR chip interface features three wait state 32 bit reads and writes.

This document discusses DRAM controller theory with interleaving, and a basic slave read/write controller to the SAR. It also describes the supporting state machines, timing diagrams, and PLD equations. The  $\mu PD98401$  can operate as a master device, which allows it access to DRAM. However, when the SAR is a master device, it can only request and obtain the i960 Jx processor bus, through the use of the processor's bus arbitration facilities. In this case, upon receiving HOLD from the SAR controller, the processor asserts HOLDA and three-states its signals, which grants bus control to the SAR.

#### 1.1 Design Goals

The goal of this document is to provide a design aid for interfacing an i960 Jx processor to an NEC  $\mu$ PD98401 ATM SAR Chip. The application note defines an interface that was developed and tested on a i960 Jx processor-compliant platform, and can be plugged into a PCI expansion slot.

The platform used is the Intel Cyclone i960<sup>®</sup> Microprocessor PCI-SDK Evaluation Platform (referred to herein as the "PCI-SDK"), with an ATM Squall module and a i960 Jx processor CPU module.

Benefits of using the PCI-SDK include:

- The PCI-SDK plugs directly into a DOS-based system's PCI slot.

- While the user is working on their hardware design, code (software) for the design can be written concurrently, which saves development time.

- The design can be implemented on the PCI-SDK through a Squall module, which enhances testability.

#### 1.2 Overview

The PCI-SDK consists of a base board with connectors which accept "modules" (daughter boards) for a CPU module and a Squall module. Many CPU and Squall modules are available; refer to Section 6.0, RELATED INFORMATION (pg. 6-20) for access to additional product information.

- The CPU modules are interchangeable daughter boards for Intel's family of i960 processors.

- The Squall modules are interchangeable daughter boards. Users can use these to design custom applications, or use one of PCI-SDK's existing modules, such as an Ethernet Squall II\* module.

The PCI-SDK base board features include:

- Two SIMM sockets which support 2, 8, or 32 Mbytes of DRAM

- One Flash ROM socket

- Three 16-bit counter/timers or one 32-bit and one 16bit counter

- DIP switch-selectable CPU clock frequency, for operation from 16 MHz to 50 MHz

- DRAM controller which automatically optimizes wait states to CPU frequency and memory speed

- One RS-232 serial port

- One Centronics compatible parallel download port

- · PCI Bus Interface

The configuration used for development of this application note is:

| CPU Module:           | i960 Jx processor                            |

|-----------------------|----------------------------------------------|

| CPU Bus<br>Frequency: | 25 MHz                                       |

|                       | 2 banks of SIMMs: 60 ns, 2 Mbyte             |

| Squall Module:        | NEC μPD98401 <sup>®</sup> - based ATM module |

#### **AP-726**

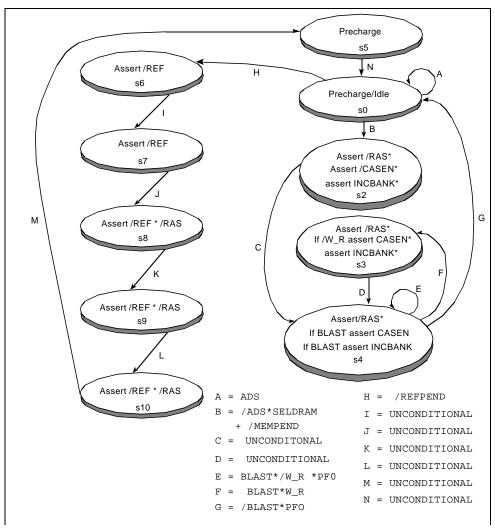

The chosen configuration simplifies the state machine for the DRAM controller (compare Figures 7 and 8).

#### 1.3 Page Mode DRAM SIMM

Page mode DRAM allows faster memory access by keeping the same row address while selecting random column addresses within that row. A new column address is selected by deasserting  $\overline{\text{CAS}}$  while keeping  $\overline{\text{RAS}}$  active, then asserting  $\overline{\text{CAS}}$  with the new column address valid to the DRAM. Page mode operation works very well with burst buses, such as the i960 Jx processor bus, in which a single address cycle can be followed by up to four data cycles.

The DRAM SIMM has four  $\overline{\text{CAS}}$  lines, one for each of eight (nine) bits in a 32-bit (36-bit) SIMM module. The four  $\overline{\text{CAS}}$  lines control the writing to individual bytes within each SIMM.

#### 1.4 DRAM Refresh

To maintain their data, the DRAM must be refreshed every 16  $\mu s.$  This is achieved by a 6-bit refresh counter embedded in the DRAM controller, driven by a 4 MHz clock. The 4 MHz clock is created by dividing a 16 MHz clock in half, twice. This corresponds to a refresh every 64 cycles of the 4 MHz clock, or approximately 400 cycles of the 25 MHz clock. The type refresh used is  $\overline{CAS}$  before  $\overline{RAS}$  ( $\overline{CAS}$  signal asserted before the  $\overline{RAS}$  signal) for specified lengths of time. Both banks of DRAM are refreshed at the same time.

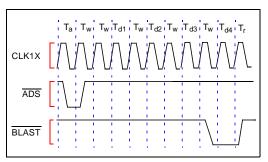

#### 1.5 Burst Capabilities for a 32-bit Bus

The i960 Jx processor can access up to four data words per request. A request starts when the processor asserts  $\overline{ADS}$  in the address cycle and ends when the processor asserts  $\overline{BLAST}$  in the last data cycle. Figure 1 shows  $\overline{ADS}$  and  $\overline{BLAST}$  timings for a quad-word write request.

Figure 1. Quad-Word Write Request with 2,1,1,1

Wait State Profile

The processor's burst capabilities on a 32-bit bus include:

- Quad-word and triple-word requests start on quad-word boundaries (A3 = 0, A2 = 0).

- Double-word requests start on double-word boundaries (A3 = X, A2 = 0).

- Single-word requests can start on any word boundary (A3 = X, A2 = X).

- Any request starting on an odd word boundary never bursts (A3 = X, A2 = 1).

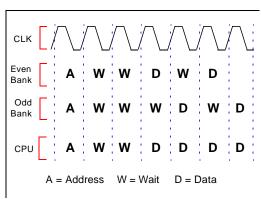

#### 1.6 Bank Interleaving

Bank interleaving allows the second, third and fourth accesses of a burst read to occur in zero wait states. The first data access must still "pay" the entire access penalty. Interleaving significantly improves memory system performance by overlapping accesses to consecutive addresses. Two-way interleaving is accomplished by dividing the memory into two 32-bit banks (also referred to as "leaves"):

- one bank for even word addresses (A2=0)

- one bank for odd word addresses (A2=1)

The two banks are read in parallel and the data from the two banks is multiplexed into the processor's data bus. Multiplexing is implemented via  $\overline{CASAx}$  and  $\overline{CASBx}$ .  $\overline{CAS}$  signals, in addition to being the Column Address Strobes, are also output enable signals for the DRAM.

Figure 2 shows DRAM with a 2-1-1-1 quad word burst read wait state profile interleaved to generate a 2-0-0-0 wait state system.

Figure 2. Two-Way Interleaving

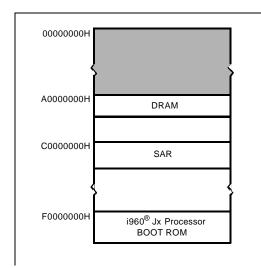

#### 1.7 i960 Jx Processor Address Mapping

Figure 3 portrays the memory map for the i960 Jx processor to SAR interface. The DRAM beginning location is set at A0000000H and the SAR beginning location is set at C0000000H. When configuring the processor's memory regions using the PMCON registers, make sure regions PMCON10\_11 and PMCON12\_13 are set for 32 bit wide bus accesses.

Figure 3. 80960Jx Interface Memory Map

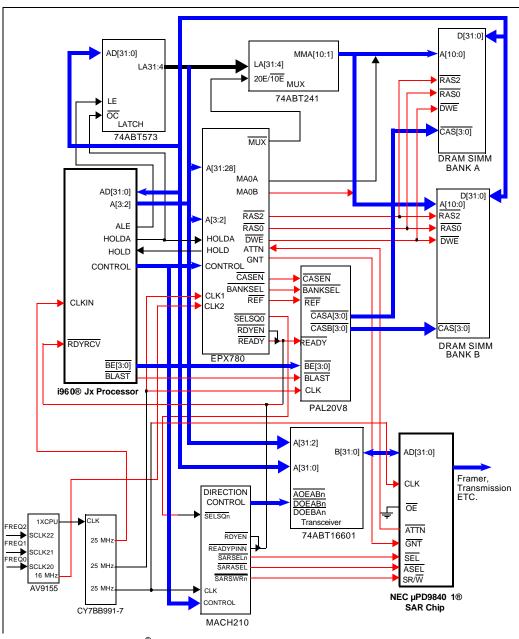

#### 2.0 CIRCUIT DESCRIPTION

Figure 4 shows a block diagram of the i960 Jx processor, interfaced to DRAM and the SAR. It can be separated into four logical blocks: clock generation, address latches, DRAM controller, and SAR slave controller. These blocks are described in the following subsections.

#### 2.1 Clock Generation

The 25 MHz CPU clock, based on the FREQ[2:0] frequency switches, is generated from an AV9155-01. The AV9155-01 feeds the 25 MHz clock into a CY7BB991-7 with an internal PLL. Also, the AV9155-01 directly generates the 16 MHz clock that is later divided down to 4 MHz, used for DRAM refresh generation.

Clock distribution is performed by the CY7BB991-7. Seperate output clocks from this device are distributed back to the CPU module, Squall II Module, and on-board logic. This device guarantees a maximum skew of  $\pm 250$  ps between outputs, and  $\pm 500$  ps between the inputs and outputs. Therefore, all clocks on the board are within  $\pm 1$  ns, making the design work very straightforward. All clock signals are terminated with 22 ohm series resistors.

#### 2.2 System Address Latches

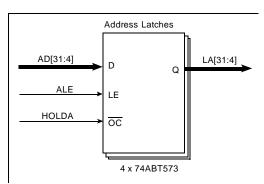

The i960 Jx processor has a multiplexed bus; therefore, address latches are needed to demultiplex the bus for use in accessing the DRAM. The latches, shown in Figure 5, capture the upper 28 address bits of the bus during the processor's address cycle, then holds them until the access is over. ALE provides the signal for latching, and HOLDA controls the output enables of the latches. HOLDA isolates the address latches from the system bus when the SAR uses the bus as a master device. As a master device, the SAR requests the bus with HOLD; the processor grants the bus with HOLDA. When HOLDA is high, the outputs to the latches are three-stated.

Figure 4. i960<sup>®</sup> Jx Processor to DRAM / NEC μPD98401 SAR Bus Interface

Figure 5. System Address Latches

#### 2.3 DRAM Controller

The DRAM controller can be separated into four sections: control logic, address flow logic, data flow logic, and DRAM controller state machines and signals. See Figure 4.

#### 2.3.1 Control Logic

The control logic is implemented using an EPX780 FPGA and a 20V8 PAL. The FPGA, the main component of the DRAM controller, supplies:

- RAS lines and read/write signals directly to the DRAM

- address bits to each DRAM bank that increments the column address

- · logic to control the address path to the DRAM

The 20V8 PAL, with direction from the FPGA, provides all the necessary logic to generate the  $\overline{\text{CAS}}$  signals for the DRAM.

#### 2.3.2 Address Flow Logic

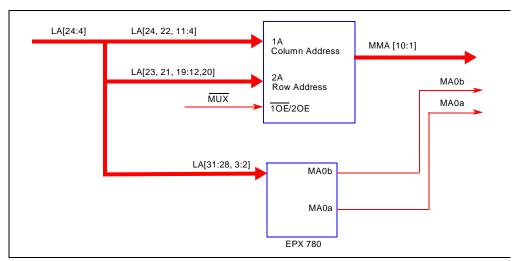

Figure 6 shows the DRAM address flow logic. The address flow logic to the DRAM is controlled by three 74ABT241 octal buffers, configured as a 12-input, two-line to one-line multiplexer. The  $\overline{\text{MUX}}$  select signal, which controls the multiplexing function, is supplied by the FPGA. The multiplexers divide the latched address bus into two addresses: the row address consisting of the latched address' higher order bits, and the column address consisting of the latched address' lower order bits.

Both row and column addresses are transferred to DRAM via the MMA[10:1] address bus. MA0a connects to A0 of the bank A DRAM, MA0b connects to A0 of the bank B DRAM.

Figure 6. DRAM Address Flow Logic

#### 2.3.3 Data Flow Logic

As indicated in Figure 4, the data path is fairly simple; it's connected directly to the DRAM from the processor, requiring no transceivers or multiplexers to control data flow between the banks. Data flow is controlled by the  $\overline{CAS}$  lines. When one bank is selected  $(\overline{CAS}$  lines asserted) the other bank is de-selected  $(\overline{CAS}$  lines deasserted). Data is output by the DRAM during a read or accepted by the DRAM during a write by the assertion  $\overline{CAS}$ .

#### 2.3.4 State Machines and Signals

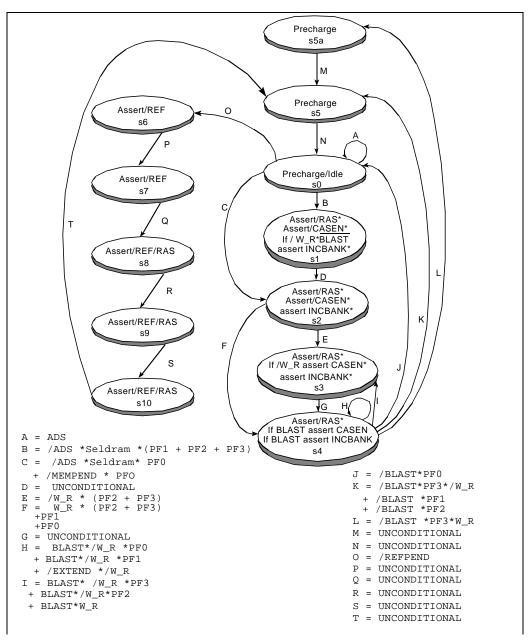

Figure 7 shows the DRAM control state machine for the PCI-SDK; Figure 8 shows a simplified version. The simplified version is the result of choosing the configuration discussed in Section 1.2, Overview (pg. 1-1). For this configuration, the CPU module Frequency Switches are set to 25 MHz (Positions 1-4 should be OFF, OFF, ON, ON. This maps to a logic 1,1,0,0. Refer to Cyclone documentation for definitions).

The PD3 pin output from the DRAM SIMM, when sampled high, indicates 60 ns DRAM. With these frequency and speed settings, the signal PF0 is set high and all the other PF signals are reset low. The PCI-SDK does not use the EXTEND signal; it is tied high.

The state machine has two major paths: a refresh path and an access path. The refresh path is taken when the refresh counter indicates a refresh is needed. The access path is taken when the processor initiates an access to the address range dedicated to the DRAM.

When a conflict occurs between an access and a refresh, the refresh has priority and proceeds; a memory pending bit is set. When refresh completes, the memory pending bit causes the access to complete. The same process occurs when an access is in progress and a request for a refresh is received. A refresh pending bit is set which causes the refresh to complete when the access completes.

The DRAM state machine is developed with Intel's PLDshell Plus<sup>®</sup>. Appendix A, PLDshell FILES contains the code which implement the DRAM controller.

The state machine transitions described here use the following PLDshell conventions for logic operators. For all the following, refer to Figure 8.

| / | Represents active-low in pin declaration;<br>Boolean NOT elsewhere in file |  |

|---|----------------------------------------------------------------------------|--|

| * | Represents Boolean AND                                                     |  |

| + | Represents Boolean OR                                                      |  |

#### 2.3.4.1 DRAM Control State Machine

The DRAM control state machine, the heart of DRAM controller, resides in the FPGA. It is controlled with inputs from the processor and equations from within the controller. Its outputs are the  $\overline{RAS}$  and  $\overline{REF}$  signals, both are active low. The  $\overline{RAS}$  signals directly drive the  $\overline{RAS}$  inputs of both banks and are used to latch the row addresses into the DRAM. Two identical  $\overline{RAS}$  signals distribute the load between the two banks.  $\overline{REF}$  provides a bit to the  $\overline{REFPEND}$  state machine, indicating a refresh has begun. This resets the  $\overline{REFPEND}$  signal, so it can be set the next time a refresh is required.

The other output functions of the DRAM controller depend upon which state the DRAM control state machine is in. The following are the signals that make up the DRAM controller.

#### 2.3.4.2 SELDRAM Signal

The active high SELDRAM signal is decoded from the latched address bits LA[31:28]. When these address bits equal  $A_{16}$  during the processor's address cycle, SELDRAM is asserted indicating an access to the DRAM memory region.

#### 2.3.4.3 REFPEND Signal

The active low REFPEND signal is asserted when a refresh is requested, either during the idle state or a DRAM access. Its main function is to keep track of when a refresh is required, so the controller will not skip the refresh if it is requested during an access. It is also the bit that causes the refresh to complete first, when in conflict with an access. Since the refresh counter runs at 4 MHz, and the REFPEND signal runs on the 25 MHz, the counter output and the REFPEND signal must be synchronized. The signal used for synchronization is the REFSYNC (see Table A-1 in Appendix A) signal embedded in the controller.

Figure 7. DRAM Control State Machine

Figure 8. Simplified DRAM State Machine

#### 2.3.4.4 MEMPEND Signal

# The active low MEMPEND signal function is similar to the REFPEND signal, except it keeps track of an access when the controller is performing a refresh. It is asserted when an access is requested either during the idle state or a refresh.

#### 2.3.4.5 MUX Signal

The  $\overline{MUX}$  signal, clocked by the <u>falling edge</u> of the 25 MHz clock, controls whether a row or column address is input to DRAM. It is actually a  $\overline{RAS}$  signal delayed by a half clock cycle. The delay allows enough row address hold time ( $t_{RAH}$ ) which DRAM requires. When  $\overline{MUX}$  is high, the row address to DRAM is valid; when  $\overline{MUX}$  is low, the column address is valid.

#### 2.3.4.6 CASEN Signal

The active low  $\overline{\text{CASEN}}$  signal provides an output enable signal to the  $\overline{\text{CAS}}$  state machines, located in the PAL20V8. Its function is determined by which state the DRAM Control state machine is in:

- s0: asserted during an address cycle in which one or more are true:

- access is to the DRAM memory region

- a refresh is not pending

- an access is pending

- s2 and s3: <u>CASEN</u> is asserted when the access is a read. (Remember that PF0 is asserted, indicating the system is operating at 25 MHz with 60 ns DRAM.)

- s4: asserted during a burst read or write access EXCEPT for the last access of the burst.

#### 2.3.4.7 INCBANK and BANKSEL Signals

The active low  $\overline{BANKSEL}$  signal determines which bank will have its  $\overline{CAS}$  lines driven:

- When low, selects bank A

- · When high, selects bank B

The active low  $\overline{\text{INCBANK}}$  signal, in conjunction with the  $\overline{\text{BANKSEL}}$  signal, creates wait states by controlling the  $\overline{\text{CAS}}$  lines. When asserted low at the end of a clock cycle, the  $\overline{\text{CAS}}$  lines are asserted, thereby selecting each bank. The  $\overline{\text{INCBANK}}$  signal operates based upon which state the DRAM Control state machine is in.

- s0: asserted during an address cycle, in which one or more are true:

- access is to the DRAM memory region

- a refresh is not pending

- an access is pending

- s2: asserted if the access is a burst read, EXCEPT for the last access of the burst.

- s4: asserted during a burst read or write access, EXCEPT for the last access of the burst.

####

The active low  $\overline{CASA}$  and  $\overline{CASB}$  signals connect to the  $\overline{CAS}$  pins of DRAM banks A and B respectively. They are enabled by the  $\overline{CASEN}$  and  $\overline{BANKSEL}$  signals. With  $\overline{BANKSEL}$  low bank A is selected, with  $\overline{BANKSEL}$  high

bank B is selected. These signals serve two purposes: to latch the column addresses into the DRAM, and to provide chip selects for each bank.  $\overline{CASA3}$  and  $\overline{CASB3}$  enables the most significant byte, and  $\overline{CASA0}$  and  $\overline{CASB0}$  enable least significant byte. The byte enables,  $\overline{BE[3:0]}$  control which byte(s) to be transferred within each bank, allowing 8 and 16 bit wide data transfers.  $\overline{BE[3:0]}$  controls bytes 3-0 respectively.

#### 2.3.4.9 MA0B and MA0A Signals

MA0B and MA0A are the least significant column address bits that increment the address to DRAM banks B and A respectively, during a burst access. They are decoded from address bits A3 and A2 of the processor's bus, which increment during a burst.

#### 2.3.4.10 RDYEN Signal

The active low  $\overline{RDYEN}$  signal enables the three-state buffer that controls the  $\overline{READY}$  signal. Since the system has two controllers on it, i.e. a DRAM controller and a SAR controller, the  $\overline{READY}$  signal of the DRAM controller has to be three-stated when the SAR controller drives its  $\overline{READY}$  signal. This prevents contention between the two ready signals. The  $\overline{RDYEN}$  signal is asserted based upon which state the DRAM control state machine is in. It's asserted during states s0, s2, s3 and s4, regardless if  $\overline{READY}$  is asserted or not.

#### 2.3.4.11 READY Signal

The active low READY signal is connected to the RDYRCV pin of the processor. It indicates to the processor that data can be transferred, and that the address can be incremented if the access is a burst. It is asserted based upon which state the DRAM control state machine is in. It is asserted unconditionally in states s2 and s3. It is asserted in s4 if the access is a burst read, provided it's not the last access of the burst.

#### 2.3.4.12 DWE Signal

The active low  $\overline{\rm DWE}$  signal indicates to the DRAM that the access is a write, provided the controller is not in refresh. The write enable signal of the DRAM's must be held high during refresh.

#### 2.4 SAR slave controller

The SAR slave controller controls access to the SAR in slave mode. Reading and writing the SAR in slave mode accesses 32 bit registers that initialize and control the SAR. Referring to Figure 4, the SAR slave controller is discussed in 4 sections: control logic, address flow logic, data flow logic, and the SAR slave controller state machines and signals.

#### 2.4.1 Control Logic

The control logic is implemented using the EPX780 FPGA and a MACH210 PLD. The FPGA decodes the SAR's address space, and provides the select signal to the SAR's access state machine. The MACH210 PLD provides all the logic that makes up the SAR controller, which controls the sequencing of the SAR itself, and the signals that control the SAR's address and data transceivers.

#### 2.4.2 Address Flow Logic

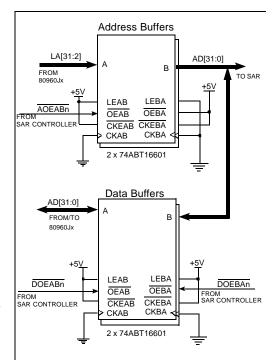

Figure 9 shows the SAR Address Buffers. The address for the SAR is controlled by two 74ABT16601 universal bus transceivers. The AOEABn control signal, output from the SAR controller, enables the latched address bits onto the multiplexed AD bus of the SAR. When inactive, the outputs of the transceivers are three-stated, allowing data to be driven on the data bus without being in contention with the address bus.

#### 2.4.3 Data Flow Logic

Figure 9 shows the SAR Data Buffers. The data for the SAR is controlled by two 74ABT16601 universal bus transceivers. The DOEABn control signal, output from the SAR controller, enables the data onto the multiplexed AD bus of the SAR, when the SAR is being written to. The DOEBAn control signal, output from the SAR controller, enables the data onto the AD bus of the processor, when the SAR is being read. When either control signal is inactive, both sides A and B of the data buffers are three-stated, allowing the bus to be used for other functions.

Figure 9. SAR Address and Data Buffers

#### 2.4.4 State Machine and Signals

The SAR slave controller consists of the SAR access state machine, and several equations that implement the control signals. The SAR controller resides in the MACH210 PLD.

The SAR controller is written in MACHXL. Appendix B, PLD EQUATIONS contain the code which implement the SAR controller. The state machine transitions described here follow the MACHXL conventions for logic operators.

| /  | Represents Boolean NOT                                              |

|----|---------------------------------------------------------------------|

| *  | Represents Boolean AND                                              |

| +  | Represents Boolean OR                                               |

| {} | Represents Substitution (OUT1=A*B*C, OUT2=A*B*C*D or OUT2={OUT1}*D) |

#### 2.4.4.1 SELC Signal

The active high SELC signal is decoded from the latched address bits LA[31:28]. When these address bits equal C<sub>16</sub> during the processor's address cycle, SELC is asserted indicating an access to the SAR memory region.

#### 2.4.4.2 SELSQ0 Signal

SELSQO is the select signal (standing for Select Squall module, remembering that the SAR is on the squall module) which initiates the SAR Access State Machine when SELC is asserted.

#### 2.4.4.3 SAR Access State Machine

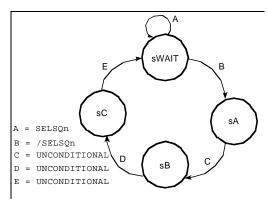

Shown in Figure 10 is the SAR access state machine. It is initiated when the SELSQO select signal from the FPGA is asserted, due to a request issued to the SAR's memory region.

The state of the control signals implemented in the controller, depend upon which state the state machine is in. The following are the signals that make up the SAR controller.

Figure 10. 80960Jx to SAR Access State Machine

#### 2.4.4.4 READYn Signal

The READYn signal is asserted on the rising edge of the clock, at the end of state sB of the SAR access state machine. At the end of state sC, READYn signals to the processor the termination of a data transfer.

#### 2.4.4.5 READYpinn Signal

The READYpinn signal is connected to the RDYRCV pin of the processor. It can be three-stated and is driven by READYn. It must be three-stated when an access other than a SAR access occurs. The READYpinn signal is paired with the READYn signal, indicated by the brackets around READYn on the right side of the READYpinn equation. (see the MACHXL PLD file of Appendix B). Pairing connects a node signal like READYn, to an output signal like READYpinn.

#### 2.4.4.6 RDYENn Signal

$\overline{RDYENn}$  controls the three-state buffer that three-states the  $\overline{READYpinn}$  signal. It is asserted when  $\overline{SELSQ0}$  is asserted.

#### 2.4.4.7 SARSELn Signal

The SARSELn signal selects the SAR, enabling it to be accessed in slave mode.

#### 2.4.4.8 SARASELn Signal

The SARASELn signal indicates to the SAR that an address is on its AD bus. On the first rising clock edge after SARASELn goes active, the SAR latches the address onto its AD bus for use during an access.

#### 2.4.4.9 SARSWRn Signal

The SARSWRn signal determines the direction of the slave access. 1=read, 0=write.

#### 2.4.4.10 AOEABn Signal

The AOEABn signal enables the B output of the SAR's address buffers, directing the flow of the latched address from the PCI-SDK, onto the AD bus of the SAR.

#### 2.4.4.11 DOEABn Signal

The DOEABn signal enables the flow of data through the data buffers from A to B, to the AD bus of the SAR during a write.

#### 2.4.4.12 DOEBAn Signal

The DOEBAn signal enables the flow of data through the data buffers from B to A, to the AD bus of the processor during a read.

#### 3.0 DRAM CONTROLLER ACCESS FLOW

This section explains how the DRAM controller is sequenced while reading, writing and refreshing the DRAM. Examples discussed are:

- · single word read access

- quad word read access

- · single word write access

- quad word write access

- refresh

For the following accesses, refer to Figure 8. All accesses to the DRAM are with the i960 Jx processor configured with a 32 bit bus.

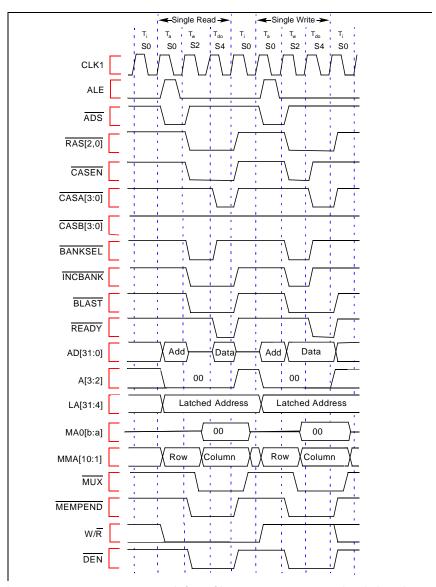

#### 3.1 Single Word Read and Write Access

Figure 11 shows a single word read timing diagram. In state s0 of the read when an access has begun, the address bits from the processor are latched, and held latched throughout the access. The MUX signal stays deasserted, selecting the row address via the multiplexer. On the clock edge at the end of state s0, the DRAM control state machine transitions to state s2. In the beginning of state s2, the BLAST signal, MEMPEND bit, INCBANK signal, and all the RAS lines are asserted. BLAST asserting at this time indicates a single access, MEMPEND indicates an access is pending, INCBANK indicates the next state is a data state, while the RAS lines load the row address into all the DRAM's. In the middle of s2 the MUX signal is asserted on the falling edge of CLK1, selecting the column address.

At the end of state s2, the state machine unconditionally transitions to state s4. In s4,  $\overline{READY}$  is asserted and the  $\overline{CAS}$  lines for bank A are asserted, based on the byte enables. Asserting of the  $\overline{CAS}$  lines enables data from the

DRAM's onto the AD bus, making state s4 the data state  $(T_{d0})$ . On the clock edge at the end of state s4, data is captured by the processor due to sampling  $\overline{READY}$  asserted. It is at this point that data put on the AD bus from the DRAM, must meet the set-up  $(t_{is1})$  and hold  $(t_{ih1})$  times of the processor. At the time  $\overline{READY}$  is sampled low,  $\overline{BLAST}$  is sampled low, causing the state machine to transition to state s0, completing the access and deasserting the  $\overline{MEMPEND}$  bit.

Figure 11 shows a single word write timing diagram. This access sequences in the same manner as the single word read access did, up until the first data state.

In state s0 of the write when an access has begun, the address bits from the processor are latched, and held latched throughout the access. The  $\overline{MUX}$  signal stays deasserted, selecting the row address via the multiplexer. On the clock edge at the end of state s0, the DRAM control state machine transitions to state s2, due to the processor access. In the beginning of state s2, the BLAST signal, MEMPEND bit,  $\overline{\text{INCBANK}}$  signal, and all the  $\overline{\text{RAS}}$  lines are asserted. BLAST asserting at this time indicates a single access, MEMPEND indicates an access is pending, INCBANK indicates the next state is a data state, while the  $\overline{RAS}$  lines load the row address into all the DRAM's. Also during state s2, data is driven on the AD bus, where it waits to be written into the DRAM's. In the middle of s2 the  $\overline{MUX}$  signal is asserted on the falling edge of CLK1, selecting the column address.

At the end of state s2, the state machine unconditionally transitions to state s4. In s4,  $\overline{READY}$  is asserted and the  $\overline{CAS}$  lines for bank A are asserted, based on the byte enables. Asserting the  $\overline{CAS}$  lines writes data into the DRAM's from the AD bus, making state s4 the data state ( $T_{d0}$ ). It is at this point that data on the AD bus must meet the set-up ( $t_{ds}$ ) and hold ( $t_{dh}$ ) times of the DRAM's. In this design,  $t_{dh}$  is most critical, and is met by holding the data on the AD bus until the end of state s4. On the clock edge at the end of state s4,  $\overline{READY}$  and  $\overline{BLAST}$  are sampled asserted, causing the state machine to transition back to state s0, completing the access and deasserting the  $\overline{MEMPEND}$  bit.

Figure 11. 80960Jx to DRAM 1 Wait State Single Word Read and Write Timing Diagram

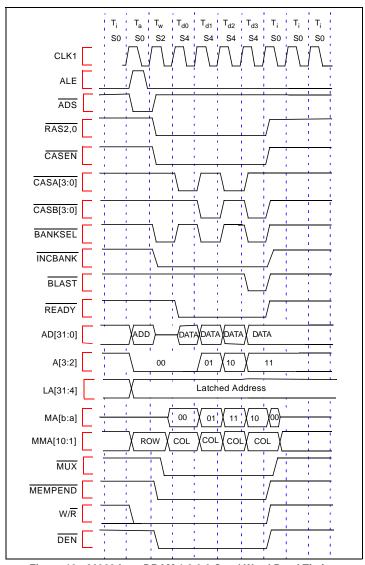

#### 3.2 Quad Word Read Access

Figure 12 shows a quad word read timing diagram. The quad word read access begins exactly the same way that the single word read access did, until the clock edge at the end of state s4. At this point, since a quad word read has 1-0-0-0 wait states, the state machine stays in s4, until a READY and BLAST are sampled asserted, on the rising clock edge at the end of state s4. As the state machine spins in s4, the toggling BANKSEL and the byte enables determine which CAS signals activate, thereby controlling which leaf of the DRAM data is transferred from. The toggling of BANKSEL causes CASA and CASB to activate alternately, with CASA enabling bank A first. As CASA and CASB alternate, bits MA0A and MA0B increment, providing two separate addresses, two for each bank. This is evident by observing Figure 12, which shows that bit "a" of MA0[b:a] toggles from 0 in data state T<sub>d0</sub> to 1 in data state T<sub>d2</sub>. This is also true with bit "b", during data states  $T_{d1}$  and  $T_{d3}$ . During these data states the MUX signal stays asserted, only allowing the  $\overline{CAS}$  address to be changed.

#### 3.3 Quad Word Write Access

Figure 13 shows a quad word write timing diagram. The quad word write access begins exactly the same way that

the single word write access did, until the clock edge at the end of state s4. At this point, since a quad word write has 1-1-1-1 wait states, the state machine alternates between states s4 and s3, with s4 being the data state (CAS signals asserted) and s3 being the wait state (CAS signals deasserted). The signals that determine which states are the data and wait states of the DRAM control state machine, are the CASEN and INCBANK signals. If at the end of s4, CASEN and INCBANK are deasserted, the CAS lines deassert and the incrementing address bits MA0[b:a] are incremented, preparing for the next data state. If at the end of s3 CASEN and INCBANK are asserted, the CAS lines are asserted and address bits MA0[b:a] are held constant until the end of the data state. The incrementing of bits MA0A and MA0B provide two separate addresses, two for each bank. This is evident by observing Figure 13, which shows that bit "a" of MA0[b:a] toggles from 0 in data state  $T_{d0}$  to 1 in data state  $T_{d2}$ . This is also true with bit "b", during data states T<sub>d1</sub> and T<sub>d3</sub>.

If the  $\overline{READY}$  and  $\overline{BLAST}$  signals are sampled asserted on the rising clock edge at the end of state s4, the state machine transitions back to state s0, where the access is complete. During these data states the  $\overline{MUX}$  signal stays asserted, only allowing the  $\overline{CAS}$  address to be changed.

Figure 12. 80960Jx to DRAM 1,0,0,0 Quad Word Read Timing

Figure 13. 80960Jx to DRAM 1,1,1,1 Quad Word Write Timing Diagram

#### 3.4 CAS before RAS Refresh

Figure 14 shows a refresh cycle timing diagram. As soon as the PCI-SDK powers up, the refresh counter starts counting, and cannot be stopped by RESET. The counter is a freerunning divide-by-64 counter, running on a 4 MHz clock. Its output switches high every 64 cycles of the 4 MHz clock, giving a 16  $\mu$ s interval for requesting refresh.

On the next 25 MHz clock edge after the output of the counter switches high, the REFSYNC signal is asserted, causing the REFCLK and REFCLKD signals to sequence as shown in Figure 14. When REFCLK is sampled high and REFCLKD is sampled low on the clock edge, REFPEND is asserted. When REFPEND is detected low on the next clock edge, the DRAM control state machine enters state s6

where refresh begins. At the beginning of s6,  $\overline{REF}$  is sserted and stays asserted through state s10. On the clock edge at the end of s6,  $\overline{REF}$  indicates to the  $\overline{REFPEND}$  state machine that the DRAM refresh is going to be satisfied, causing  $\overline{REFPEND}$  to be deasserted.

The  $\overline{REF}$  signal serves another purpose. It enables the  $\overline{CAS}$  state machines during refresh, allowing the  $\overline{CAS}$  signals to be driven. In states s8-s10, the  $\overline{RAS}$  signals are asserted, giving a  $\overline{CAS}$  before  $\overline{RAS}$  refresh, since the  $\overline{CAS}$  signals were asserted back in state s6.

After the state machine transitions out of state s10 completing the refresh, it passes through states s5 and s0, where the required RAS precharge takes place before another access can begin

Figure 14. CAS-Before-RAS Refresh Cycle

#### 4.0 SAR SLAVE ACCESS FLOW

This section describes how the SAR controller is sequenced during a single word read and write access.

All accesses to the SAR are with the i960 Jx processor configured with a 32 bit bus.

#### 4.1 Single Word Read and Write Access

Figure 15 shows the Single Word Read Access Timing Diagram. The single word access begins with the processor making a request to the SAR address space. The address is latched and decoded, asserting the SELSQO select signal. On the first rising clock edge that SELSQO is low, the SAR access state machine initiates and unconditionally transi-

tions from state sA through state sC, back into state sWAIT. The state machine will stay in sWAIT until  $\overline{SELSQ0}$  asserts, indicating another access.

At the end of state sWAIT when the state machine transitions to sA, the SAR controller drives \$\overline{SARSWRn}\$ high for a read, and asserts \$\overline{SARSELn}\$, \$\overline{SARASELn}\$, and \$\overline{AOEABn}\$. As \$\overline{AOEABn}\$ asserts, the address buffers place the address on the SAR's AD bus, where it is latched into the SAR on the first rising edge of the clock after \$\overline{SARASELn}\$ goes low. On the following clock edge after the address is latched, the SAR places the data on its AD lines, which is at the beginning of state sC, provided that \$\overline{SARSELn}\$ is low. At the beginning of state sC with the data placed on the SAR's AD bus, \$\overline{READYpinn}\$ is asserted and \$\overline{DOEBAn}\$ activates, placing the data onto the processors AD bus, through the

#### **AP-726**

data buffers. At the end of state sC, the processor samples  $\overline{READY}$  and  $\overline{BLAST}$  asserted, signaling the end of the data transfer. When  $\overline{READY}$  and  $\overline{BLAST}$  are sampled asserted during the transition from sC to sWAIT, the  $\overline{SELSQ0}$  signal deasserts, keeping the SAR access state machine in state sWAIT.

Figure 15 shows the Single Word Write Access Timing Diagram. The single word access begins with the processor making a request to the SAR address space. The address is latched and decoded, asserting the  $\overline{SELSQ0}$  select signal. On the first rising clock edge that  $\overline{SELSQ0}$  is low, the SAR access state machine initiates and unconditionally transitions from state sA through state sC, back into state sWAIT. The state machine will stay in sWAIT until  $\overline{SELSQ0}$  asserts, indicating another access.

At the end of state sWAIT when the state machine transitions to sA, the SAR controller drives  $\overline{SARSWRn}$  low for a

write, and asserts SARSELn, SARASELn, and AOEABn. As AOEABn asserts, the address buffers place the address on the SAR's AD bus, where it is latched into the SAR on the first rising edge of the clock after SARASELn goes low. On the same clock edge that the address is latched, the DOEABn signal is asserted, enabling data onto the SAR's AD bus, through the data buffers. The SAR then completes the access by latching the data present on its AD bus on the leading edge of the clock, just before SARSELn goes high. The clock edge in this case is at the end of state sB.

In the beginning of state sC after the access has completed, the controller asserts  $\overline{READYpinn}$  and deasserts  $\overline{DOEABn}$ , removing the data from the SAR's AD bus. At the end of state sC, the processor samples  $\overline{READY}$  and  $\overline{BLAST}$  asserted, signaling the end of the data transfer. When  $\overline{READY}$  and  $\overline{BLAST}$  are sampled asserted during the transition from sC to sWAIT, the  $\overline{SELSQ0}$  signal deasserts, keeping the SAR access state machine in state sWAIT.

Figure 15. 80960Jx to  $\mu PD98401$  Single Word Read and Write Timing Diagram

#### 5.0 CONCLUSION

This application note discusses how to interface between an Intel i960 Jx processor and an NEC  $\mu$ PD98401 Local ATM SAR Chip. The platform used was a Cyclone Microsystems PCI-SDK evaluation platform, with a i960 Jx processor module and an ATM Squall module. With the Squall module containing the SAR chip. To support the interface between the i960 Jx processor and the SAR chip are 2, 8, or 32 Mbytes of DRAM, implemented in two 72 pin SIMM sockets. The schematics were generated in Future Net. The PLD equations for the DRAM controller were written in PLDshell, and the SAR controller equations were written in MACHXL. The schematics and PLD files are available through Intel America's Application Support BBS.

#### 6.0 RELATED INFORMATION

To receive Intel literature, contact:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect IL 60056-7641 1-800-879-4683

Table 1. Related Information

| Reference #                                                         | Document Name                                         | Order#       |  |  |

|---------------------------------------------------------------------|-------------------------------------------------------|--------------|--|--|

| 1                                                                   | Intel Solutions960® catalog                           | Intel 270791 |  |  |

| 2                                                                   | 2 i960® Jx Microprocessor Users's Manual Intel 272483 |              |  |  |

| 3 80960JA/JF Embedded 32-bit Microprocessor Data Sheet Intel 272504 |                                                       |              |  |  |

| 4                                                                   | μPD98401 LOCAL ATM SAR CHIP User's Manual             | NEC IEU-1384 |  |  |

| 5 μPD98401 LOCAL ATM SAR CHIP Preliminary Data Sheet                |                                                       | NEC ID-3392  |  |  |

| 6 10 ns FLASHlogic FPGA with SRAM Option Data Sheet Altera          |                                                       | Altera       |  |  |

| 7                                                                   | PLDshell Plus /PLDasm User's Guide V4.0               | Intel        |  |  |

| 8                                                                   | Cyclone i960 <sup>®</sup> Microprocessor User's Guide | Intel 272577 |  |  |

| 9                                                                   | MACHXL Software Users's Guide                         | AMD          |  |  |

| 10                                                                  | MACH 1 and 2 Family Data Book                         | AMD          |  |  |

You can use your PC with modem to download schematics and PLD equations from Intel's Bulletin Board Service (BBS).

| Intel Technical Support Hotline                                       | North America:<br>Europe: | 800-628-8686<br>44-793-696-000                                       |

|-----------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------|

| Intel's Bulletin Board Service (BBS) for schematics and PLD equations | North America:<br>Europe: | 916-356-3600<br>supports up to 14.4 Kbps (n,8,1,p)<br>44-793-432-955 |

To contact Cyclone Microsystems for additional information about their products:

| Cyclone Microsystems | Phone: 203-786-5536      |

|----------------------|--------------------------|

| 25 Science Park      | FAX: 203-786-5025        |

| New Haven CT 06511   | e-mail: info@cyclone.com |

### APPENDIX A PLDshell FILES

Table A-1 contains the PLD equations used to build the portion of the DRAM controller, implemented in the Altera FLASHlogic EPX780 FPGA. Table A-2 contains the PLD equations used to build the portion of the DRAM controller, implemented in the PAL20V8. The PLD equations were created in PLDshell.

Table A-1. DRAM Controller EPX780 PLDshell File (Sheet 1 of 12)

| PATTERN D601 - Compiled with PLDShell REVISION E AUTHOR J. Smith COMPANY Cyclone Microsystems Inc. DATE 5-10-95  CHIP DCTRL iFX780_84  PIN 3 pclk ;INP: system clock PIN 45 clk16 ;INP: 16MHz clock PIN 51 rst ;INP: reset PIN 47 ads ;INP: PIN 81 blast ;INP: PIN 81 blast ;INP: PIN 55 a31 ;INP: PIN 56 a30 ;INP: PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 64 a18 ;INP: PIN 64 a18 ;INP: PIN 32 a3 ;INP: address to increment PIN 13 a2 ;INP: select bank cas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| AUTHOR J. Smith  COMPANY Cyclone Microsystems Inc.  DATE 5-10-95  CHIP DCTRL iFX780_84  PIN 3 pclk ;INP: system clock  PIN 45 clk16 ;INP: 16MHz clock  PIN 51 rst ;INP: reset  PIN 47 ads ;INP:  PIN 81 blast ;INP:  PIN 85 a31 ;INP:  PIN 56 a30 ;INP:  PIN 56 a30 ;INP:  PIN 58 a29 ;INP:  PIN 60 a28 ;INP:  PIN 62 a19 ;INP:  PIN 64 a18 ;INP:  PIN 64 a18 ;INP:  PIN 64 a18 ;INP:  PIN 64 a28 ;INP:  PIN 65 a30 ;INP:  PIN 66 a28 ;INP:  PIN 67 a28 ;INP:  PIN 68 a29 ;INP:  PIN 69 a28 ;INP:  PIN 69 a38 ;INP: |          |

| COMPANY Cyclone Microsystems Inc.  DATE 5-10-95  CHIP DCTRL iFX780_84  PIN 3 pclk ;INP: system clock PIN 45 clk16 ;INP: 16MHz clock PIN 51 rst ;INP: reset PIN 47 ads ;INP: PIN 81 blast ;INP: PIN 85 a31 ;INP: PIN 56 a30 ;INP: PIN 56 a30 ;INP: PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 64 a18 ;INP: PIN 64 a28 ;INP: PIN 65 a30 ;INP:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| DATE 5-10-95  CHIP DCTRL iFX780_84  PIN 3 pclk ;INP: system clock PIN 45 clk16 ;INP: 16MHz clock PIN 51 rst ;INP: reset PIN 47 ads ;INP: PIN 81 blast ;INP: PIN 55 a31 ;INP: PIN 56 a30 ;INP: PIN 58 a29 ;INP: PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 64 a18 ;INP: PIN 64 a28 ;INP: PIN 65 a30 ;INP:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| DATE 5-10-95  CHIP DCTRL iFX780_84  PIN 3 pclk ;INP: system clock PIN 45 clk16 ;INP: 16MHz clock PIN 51 rst ;INP: reset PIN 47 ads ;INP: PIN 81 blast ;INP: PIN 55 a31 ;INP: PIN 56 a30 ;INP: PIN 58 a29 ;INP: PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 64 a18 ;INP: PIN 64 a28 ;INP: PIN 65 a30 ;INP:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| PIN       3       pclk       ;INP: system clock         PIN       45       clk16       ;INP: 16MHz clock         PIN       51       rst       ;INP: reset         PIN       47       ads       ;INP:         PIN       81       blast       ;INP:         PIN       55       a31       ;INP:         PIN       56       a30       ;INP:         PIN       58       a29       ;INP:         PIN       60       a28       ;INP:         PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| PIN       3       pclk       ;INP: system clock         PIN       45       clk16       ;INP: 16MHz clock         PIN       51       rst       ;INP: reset         PIN       47       ads       ;INP:         PIN       81       blast       ;INP:         PIN       55       a31       ;INP:         PIN       56       a30       ;INP:         PIN       58       a29       ;INP:         PIN       60       a28       ;INP:         PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| PIN       45       clk16       ;INP: 16MHz clock         PIN       51       rst       ;INP: reset         PIN       47       ads       ;INP:         PIN       81       blast       ;INP:         PIN       55       a31       ;INP:         PIN       56       a30       ;INP:         PIN       58       a29       ;INP:         PIN       60       a28       ;INP:         PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| PIN 45 clk16 ;INP: 16MHz clock PIN 51 rst ;INP: reset PIN 47 ads ;INP: PIN 81 blast ;INP: PIN 55 a31 ;INP: PIN 56 a30 ;INP: PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 32 a3 ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| PIN       45       clk16       ;INP: 16MHz clock         PIN       51       rst       ;INP: reset         PIN       47       ads       ;INP:         PIN       81       blast       ;INP:         PIN       55       a31       ;INP:         PIN       56       a30       ;INP:         PIN       58       a29       ;INP:         PIN       60       a28       ;INP:         PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| PIN       51       rst       ;INP: reset         PIN       47       ads       ;INP:         PIN       81       blast       ;INP:         PIN       55       a31       ;INP:         PIN       56       a30       ;INP:         PIN       58       a29       ;INP:         PIN       60       a28       ;INP:         PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

| PIN       47       ads       ;INP:         PIN       81       blast       ;INP:         PIN       55       a31       ;INP:         PIN       56       a30       ;INP:         PIN       58       a29       ;INP:         PIN       60       a28       ;INP:         PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| PIN       81       blast       ;INP:         PIN       55       a31       ;INP:         PIN       56       a30       ;INP:         PIN       58       a29       ;INP:         PIN       60       a28       ;INP:         PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| PIN 55 a31 ;INP: PIN 56 a30 ;INP: PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 32 a3 ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| PIN 56 a30 ;INP: PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 32 a3 ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| PIN 58 a29 ;INP: PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 32 a3 ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| PIN 60 a28 ;INP: PIN 62 a19 ;INP: PIN 64 a18 ;INP: PIN 32 a3 ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| PIN       62       a19       ;INP:         PIN       64       a18       ;INP:         PIN       32       a3       ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| PIN 64 al8 ;INP:<br>PIN 32 a3 ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| PIN 32 a3 ;INP: address to increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| PIN 13 a2 ;INP: select bank cas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| PIN 20 al ;INP: select bank cas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |