# 28F008S5 SPECIFICATION UPDATE

Release Date: February 1997

Order Number: 297796-003

The 28F008S5 may contain design defects or errors known as errata. Characterized errata that may cause the behavior of these products to deviate from published specifications are documented in this specification update.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

\* Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call in North America 1-800-879-4683, Europe 44-0-1793-431-155, France 44-0-1793-421-777,

Germany 44-0-1793-421-333 other Countries 708-296-9333

Copyright © 1997, Intel Corporation

ii February, 1997 297796-003

# **CONTENTS**

| REVISION HISTORY             | 1  |

|------------------------------|----|

| PREFACE                      | 2  |

| SUMMARY TABLES OF CHANGES    | 3  |

| IDENTIFICATION INFORMATION   | 6  |

| ERRATA                       | 7  |

| SPECIFICATION CHANGES        | 12 |

| SPECIFICATION CLARIFICATIONS | 12 |

| DOCUMENTATION CHANGES        | 12 |

# **REVISION HISTORY**

| Date of Revision | Version | Description                                                        |

|------------------|---------|--------------------------------------------------------------------|

| 09/10/96         | -001    | Document includes all known errata to date (original version).     |

| 12/01/96         | -002    | Removed CE# glitch sensitivity erratum. Added RP# Control erratum. |

| 02/01/97         | -003    | Added I <sub>PPS</sub> erratum.                                    |

#### **PREFACE**

As of July, 1996, Intel's Computing Enhancement Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This is the third release of the 28F008S5 Specification Update. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain additional information that was not previously published. Functional descriptions for this product are found in the *Byte-Wide Smart 5 FlashFile™ Memory Family 4-, 8- and 16-Mbit Datasheet.*

#### Affected Documents/Related Documents

| Title                                                                 | Order  |

|-----------------------------------------------------------------------|--------|

| Byte-Wide Smart 5 FlashFile™ Memory Family 4, 8 and 16 Mbit Datasheet | 290597 |

### Nomenclature

**Errata** are design defects or errors. These may cause the behavior of these products to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes** are modifications to the current published specifications.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation.

**Documentation Changes** include typos, errors, or omissions from the current published specifications.

#### NOTE:

Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

#### SUMMARY TABLES OF CHANGES

The following tables indicate the Specification Changes, Errata, Specification Clarifications, or Documentation Changes which apply to the *Byte-Wide Smart 5 FlashFile™ Memory Family 4-, 8-Mbit and 16-Mbit Datasheet.* Intel may fix some of the errata in a future stepping of the component, and to account for the other outstanding issues through documentation or specification changes as noted. These tables use the following notations:

# Codes Used in Summary Tables

# Steps

X: Errata exists in the stepping indicated. Specification

Change or Clarification that applies to this stepping.

(No mark)

or (Blank box): This erratum is fixed in listed stepping or specification

change does not apply to listed stepping.

Page

(Page): Page location of item in this document.

Status

Doc: Document change or update will be implemented.

Fix: This erratum is intended to be fixed in a future step of the

component.

Fixed: This erratum has been previously fixed.

NoFix: There are no plans to fix this erratum.

Eval: Plans to fix this erratum are under evaluation.

Row

Change bar to left of table row indicates this erratum is

either new or modified from the previous version of the

document.

# Errata

|        | Steppings |     |     |      |                                 |                                 |

|--------|-----------|-----|-----|------|---------------------------------|---------------------------------|

| Number | A-1, -3   | A-6 | A-8 | Page | Status                          | Errata                          |

| 1      | Х         | Χ   | Х   | 7    | Fix                             | Deep Power-Down Current         |

| 2      | Х         | Х   | Х   | 8    | Fix                             | Block Locking and Unlocking     |

| 3      | Х         |     |     | 9    | Fixed CE# Glitch Sensitivity    |                                 |

| 4      | Х         | Х   | Х   | 11   | Fix RP# Control during Power-Up |                                 |

| 5      | Х         | Х   | Х   | 12   | Eval                            | V <sub>PP</sub> Standby Current |

# Specification Changes

|        | Steppings       |  |      |        |                       |                                             |

|--------|-----------------|--|------|--------|-----------------------|---------------------------------------------|

| Number | A-1, -3 A-6 A-8 |  | Page | Status | Specification Changes |                                             |

| N/A    |                 |  |      | 12     |                       | None in this Specification Update revision. |

# Specification Clarifications

|        | Steppings |     |     |      |        |                                             |

|--------|-----------|-----|-----|------|--------|---------------------------------------------|

| Number | A-1, -3   | A-6 | A-8 | Page | Status | Specification Clarifications                |

| N/A    |           |     |     | 12   |        | None in this Specification Update revision. |

# **Documentation Changes**

| Number | Document Revision | Page | Status | Documentation Changes                       |

|--------|-------------------|------|--------|---------------------------------------------|

| N/A    |                   | 12   |        | None in this Specification Update revision. |

# **IDENTIFICATION INFORMATION**

# Markings

The Finished Processing Order (FPO) number correlates to a specific device stepping as illustrated in the table below:

| Stepping <sup>(1,2)</sup> | Identifier                                                      |

|---------------------------|-----------------------------------------------------------------|

| A-1,-3                    | Ninth digit on topside FPO mark (third line) = J, K, L, M, or N |

| A-6                       | Ninth digit on topside FPO mark (third line) = P or Q           |

| A-8                       | Ninth digit on topside FPO mark (third line) = U or V           |

#### NOTE:

- Device steppings are based on continuous updates made in manufacturing and testing of the device and represent the current material shipped.

- 2. A-0, -2, -4, -5, and -7 material was never sampled.

# **ERRATA**

# 1. Deep Power-Down Current

**PROBLEM:** I<sub>CCD</sub> deviates from the published specification. Please replace the existing *Byte-Wide Smart 5 FlashFile™ Memory Family 4-, 8- and 16-Mbit Datasheet* I<sub>CCD</sub> specification with the following information:

|                  |                                            |       | 5.0V V <sub>CC</sub> |     |      | Test                                                     |

|------------------|--------------------------------------------|-------|----------------------|-----|------|----------------------------------------------------------|

| Sym              | Parameter                                  | Notes | Тур                  | Max | Unit | Conditions                                               |

| I <sub>CCD</sub> | V <sub>CC</sub> Deep Power-Down<br>Current | 1     |                      | 16  | μΑ   | $RP\# = GND \pm 0.2V$ $I_{OUT} (RY/BY\#) = 0 \text{ mA}$ |

#### NOTE:

**IMPLICATION:** The increased current requirements may have an impact on power supply loading or battery life.

WORKAROUND: None.

**STATUS:** A fix for this erratum has been identified and will be implemented in the next component stepping. Refer to Summary Table of Contents to determine the affected stepping.

**AFFECTED PRODUCTS:** A-1, -3, -6, and -8 steppings are affected by this erratum.

All currents are in RMS unless otherwise noted. These currents are valid for all product versions (packages and speeds).

# 2. Block Locking and Unlocking

**PROBLEM:** The block locking and unlocking security feature is currently nonfunctional. Attempts to lock and unlock blocks may cause subsequent byte write and/or block erase failures. If a subsequent operation fails, a device protection error will cause the problem. The component incorrectly reads a block lock-bit as being set when it is actually cleared.

**IMPLICATION:** Block locking feature is disabled. This erratum affects the following commands: Set Master Lock-Bit, Set Block Lock-Bits, and Clear Block Lock-Bits.

**WORKAROUND:** To prevent the accentual setting and clear of block lock-bits, Intel sets the Master Lock-Bit during the test flow. This disables the ability to lock and unlock block via software only. However, blocks can still be locked and unlocked if 12V is applied to the component's RP# input. To prevent this from occurring, do not apply 12V to the RP# input.

If data security is of utmost importance, lower  $V_{PP}$  voltage equal to or less than  $V_{PPLK}$  during normal operations. With  $V_{PP}$  equal to or less  $V_{PPLK}$ , the device is protected against all data manipulation operations.

**STATUS:** A fix for this erratum has been identified and will be implemented in the next component stepping. Refer to Summary Table of Contents to determine the affected stepping.

**AFFECTED PRODUCTS:** A-1, -3, -6, and steppings are affected by this erratum.

## 3. CE# Glitch Sensitivity

**PROBLEM:** A noisy CE# control signal may cause an invalid read. This erroneous read only occurs after the device has received over one hundred consecutive short CE# glitches (t<sub>EHEL</sub> < 65 ns) with intermittent CE#-high time (t<sub>EHEL</sub>) greater than 145 ns (see the figure below, *A Long Series of CE# Glitches May Induce an Invalid Read*).

A Long Series of CE# Glitches May Induce an Invalid Read

After valid data is read, the device must receive another series of CE# glitches (typically over one hundred) to induce an invalid read. CE# glitches sequences, other than defined in the above figure, A Long Series of CE# Glitches May Induce an Invalid Read, have no adverse effect.

297796-003 February, 1997 9 of 12

**IMPLICATION:** This erratum may affect read operations in systems that have a lot of noise on the flash memory's CE# input. If CE# is generated asynchronously from the upper address lines, noise on CE# can sometimes occur when upper address lines transition from one state to another. However, applications that access flash memory sequentially will have stable upper address lines and will therefore produce fewer CE# glitches. Systems that execute code from flash memory or download code from flash memory into DRAM will usually access the device sequentially; therefore, they will be less susceptible to this erratum.

Carefully analyze the flash memory CE# input. If no glitches are seen on this signal when accessing other devices, your system does not have a problem. If glitches are detected, more in-depth system characterization is need to identify susceptibility to this erratum.

It is important to understand how these glitches manifest themselves in order to determine whether or not they will cause a problem.

1. In systems that flow unlatched addresses to CE# control logic, the decode logic may generate CE# glitches when the address bus transitions from one state to another. However, the  $\mu P/\mu C$  address switching frequency is usually very fast (somewhere in the order of 1/2 the  $\mu P/\mu C$  operating frequency) which will cause the glitches high time to be less than 145 ns. If the CE#-high time is less than 145 ns, the glitch has no effect on the component.

Note: Most  $\mu P/\mu C$  with integrated chip select logic use latched outputs and therefore may not have CE# glitches.

If the address bus is not pulled up or pulled down during idle bus cycles, the address bus may be left in an undetermined state. This condition may cause CE# glitches.

**WORKAROUND:** If it is determined that the CE# causes a problem, possible solutions to help workaround this erratum are suggested as follows:

#### Hardware solution:

Add system logic to prevent CE# glitches such as latched CE# control logic or pullup/pulldown resistors to the address bus.

#### Software solution for data storage applications:

If the device receives over one hundred consecutive CE# glitches, issue a Byte Write command and program FFh to any location before executing a read operation. Programming FFh will not alter stored data, but it will give the component sufficient time to prepare for the read operation.

**STATUS:** This erratum has been fixed. Refer to Summary Table of Contents to determine the affected steppings.

**AFFECTED PRODUCTS:** A-1 and -3 steppings are affected by this erratum.

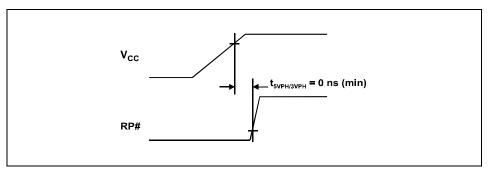

# 4. RP# Control during Power-Up

**PROBLEM:** RP# must be held low while V<sub>CC</sub> ramps to a valid level during power transitions.

Hold RP# Active While V<sub>CC</sub> Ramps

Holding RP# low during power-up blocks spurious write initiated by system control logic which may occur as the system voltage transitions to a stable level. Intel recommends the usage of RP# for CPU/memory reset synchronization, write protection, and deep power-down mode.

**IMPLICATION:** This erratum only affects power-up operations. Systems that tie the flash memory's RP# input to the system RESET# signal typically will not have a problem with erratum because the RESET# signal is usually held low during the power-up sequence to properly synchronize the CPU. However, systems that ties RP# directly to  $V_{CC}$  will be more exposed to this problem. So, carefully analyze RP# during the power-up condition to fully understand its behavior.

**WORKAROUND:** If it is determined that this erratum may cause a problem, here is a possible workaround.

Use a simple RC delay network to hold RP# low during the power-up condition or tie the RP# input to the system RESET# signal. This workaround will eliminate your exposure to this problem and also provide your design with additional power-up security.

297796-003 February, 1997 11 of 12

**STATUS:** A fix for this erratum has been identified and will be implemented in the next component stepping. Refer to Summary Table of Contents to determine the affected stepping.

AFFECTED PRODUCTS: A-1, -3, -6, and -8 steppings are affected by this erratum.

## 5. V<sub>PP</sub> Standby Current

**PROBLEM:** With V<sub>PP</sub> at GND, I<sub>PPS</sub> deviates from the published value. This deviation only affects the negative current specification listed in the datasheet. The positive current value, +15  $\mu$ A, remains valid. See the table below for the modified negative I<sub>PPS</sub> current specification.

|                  |                                 |       | 5.0V V <sub>CC</sub> |      | 5.0V V <sub>CC</sub> |                       |  | Test |

|------------------|---------------------------------|-------|----------------------|------|----------------------|-----------------------|--|------|

| Sym              | Parameter                       | Notes | Тур                  | Max  | Unit                 | Conditions            |  |      |

| I <sub>PPS</sub> | V <sub>PP</sub> Standby Current | 1     |                      | -300 | μΑ                   | V <sub>PP</sub> = GND |  |      |

#### NOTE:

All currents are in RMS unless otherwise noted. These currents are valid for all product versions (packages and speeds).

If  $V_{PP}$  is greater than or equal to  $V_{CC}$ ,  $I_{PPS}$  adheres to the datasheet specification of  $\pm 15~\mu A$ .

**IMPLICATION:** This erratum only affects systems that switch V<sub>PP</sub> to GND.

WORKAROUND: None.

**STATUS:** Plans to fix this erratum are under evaluation. Refer to Summary Table of Contents to determine the affected stepping.

AFFECTED PRODUCTS: A-1, -3, -6, and -8 steppings are affected by this erratum.

#### SPECIFICATION CHANGES

There are no specification changes in this Specification Update revision.

#### SPECIFICATION CLARIFICATIONS

There are no specification clarifications in this Specification Update revision.

### **DOCUMENTATION CHANGES**

There are no documentation changes in this Specification Update revision.