# AP-617 APPLICATION

**NOTE**

## Additional Flash Data Protection Using VPP, RP#, and WP#

MICHAEL CASTILLO MCD MARKETING APPLICATIONS

November 1995

Order Number: 292172-001

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

© INTEL CORPORATION 1995 CG-041493

### 1.0 INTRODUCTION

The introduction of reprogrammable, nonvolatile memory necessitates measures to protect stored information. Intel's Flash memory offers many advanced features to protect data integrity. Internal circuitry can help protect data at power-up, preventing spurious writes caused by power or signal glitches. Control pins, such as Reset Power-Down (RP#), Write Protect (WP#), Chip Enable (CE#), and Write Enable (WE#) inherently protect data integrity and control data flow. In today's diverse applications, system designers may desire to add optional circuitry to exploit these features. For example, general purpose I/O lines can be used to control write capability to the flash device.

This application note will first examine the functions of Vpp, RP#, and WP# for the boot block devices. Other devices, such as the 28F016 FlashFile $^{\rm TM}$  memory, offer similar features. Several optional system-level circuit solutions which utilize Vpp and RP# to increase write control will then be discussed. Finally, microcontroller reset timings will be addressed. A brief discussion of boot block and FlashFile architectures is included in Appendix A. Table 1 provides an index of the write protection options available to each Intel Flash memory component.

Table 1. Control Circuit Index by Flash Density

| Table 1. Control Circuit lindex by Flash Density |                                                                                                |          |  |  |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| Density                                          | Available Options                                                                              | Section  |  |  |  |  |

| 28F256, 28F512,<br>28F010, 28F020                | V <sub>PP</sub>                                                                                | 3.1      |  |  |  |  |

| 28F001BX,<br>28F200/002BX,<br>28F400/004BX       | V <sub>PP</sub> , RP#                                                                          | 3.1, 5.1 |  |  |  |  |

| 28F200/002BV,<br>28F400/004BV,<br>28F800/008BV   | V <sub>PP</sub> , RP#, WP#                                                                     | 3.1, 5.1 |  |  |  |  |

| 28F008SA                                         | V <sub>PP</sub> , RP#                                                                          | 3.1, 5.1 |  |  |  |  |

| 28F016SA/SV,<br>28F016XS/XD,<br>28F032SA         | V <sub>PP</sub> , RP#, WP#, and<br>Software<br>(See 16-Mbit Flash<br>Product User's<br>Manual) | 3.1      |  |  |  |  |

### 2.0 FLASH DATA PROTECTION AND EXTERNAL CONTROL MECHANISMS

Intel Flash provides several mechanisms to prevent unintentional writes. This protection is built into, and inherent to, the functions of  $V_{PP}$ ,  $V_{CC}$ , RP#, WP#, and CE#. The same circuits that prevent unintentional writes make these signals well-suited for optional control circuits. In the following sections, the functions of  $V_{PP}$ , RP#, and WP# will be examined along with circuits which use these signals for greater write control.

Many systems do not need additional protection since Intel Flash inherently provides a level of protection. However, in some circumstances additional protection might be considered necessary. Unlike other types of memory, flash retains data after power has been removed. Thus, any inadvertent writes to flash are retained. Alternatively, a write to flash could place the device into a mode other than read, thus potentially preventing the system from booting properly. Flash is most vulnerable in three main circumstances:

- Unstable control signals during power-up and power-down

- During the execution of runaway code

- Control signal glitches during steady-state operation

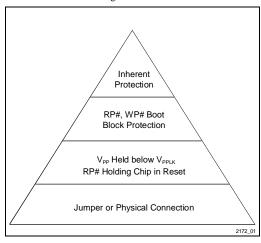

Figure 1 shows the various levels of write protection available for use in designs.

Figure 1. Various Levels of Protection May Be Added to Flash

### 3.0 VPP CHARACTERISTICS

V<sub>PP</sub> provides power to the flash device for write and erase operations and has traditionally required an external 12V supply. Just as gasoline fuels a car engine, V<sub>PP</sub> provides the gas that allows the chip to execute a write operation. Without gasoline, the car engine won't run. Similarly, without this necessary supply voltage, flash cannot write. While newer SmartVoltage flash devices provide program and erase operations at 5V as well as 12V, the V<sub>PP</sub> pin has been retained in the pinout for the following reasons:

- Provide a means of absolute protection when grounding V<sub>PP</sub>

- Maintain compliance with JEDEC dual supply standards

- Ensure easy migration for current flash-based systems

- Provide designers with maximum procurement flexibility

SmartVoltage allows system designers to tie the  $V_{PP}$  pin to  $V_{CC}$  for single voltage designs.

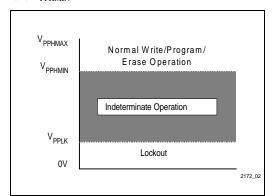

The range of DC operation for V<sub>PP</sub> is valid within either the write lockout range between 0V to V<sub>PPLK</sub> (V<sub>PPLMIN</sub> for some devices) or the program and erase range of V<sub>PPHMIN</sub> to V<sub>PPHMAX</sub>, as shown in Figure 2. During a write or erase, V<sub>PP</sub> must sustain at least a voltage of V<sub>PPHMIN</sub>. Furthermore, the flash device locks out all write and erase operations when V<sub>PP</sub> is below V<sub>PPLK</sub>. Finally, write and erase operations are not guaranteed when V<sub>PP</sub> is within the range of voltages between V<sub>PPLK</sub> and V<sub>PPHMIN</sub>.

Figure 2. When V<sub>PP</sub> Resides below V<sub>PPLK</sub> Program and Erase Commands to the Flash Device Are Prevented

$V_{PP}$  provides protection against spurious writes by locking out all write and erase operations when  $V_{PP}$  resides in the write lockout range between 0V and  $V_{PPLK}$ . Any attempted writes or erases, when in this condition, will result in an error recorded in the Status Register. Read operations remain unaffected by  $V_{PP}$ .

Since  $V_{PP}$  may be tied directly to the system's voltage source, effort should be taken to ensure that the source supply voltage stays within specified tolerance levels. For most flash devices operating at 12V,  $V_{PP}$  tolerance is  $\pm 5\%$  1. SmartVoltage flash devices operating at 5V offer a  $\pm 10\%$  tolerance.

For SmartVoltage products, the device automatically senses the voltage supplied to  $V_{PP}$  during power-up or reset recovery. If the flash device senses that the source is 5V, within the 5V  $\pm 10\%$  range ( $V_{PPH1}$ ), on-chip charge pumps are enabled for program and erase operations. If  $V_{PP}$  is within the 12V  $\pm 5\%$  range ( $V_{PPH2}$ ), on-chip charge pumps are disabled and the external voltage is used

Although  $V_{PP}$  was designed to lock out writes and erases that may occur at power-up ( $V_{PPLK}$  specification),  $V_{PP}$  may also be used to add protection to a system. To implement this protection, a designer could connect a logic controlled circuit that drops  $V_{PP}$  below  $V_{PPLK}$  to prevent writes. For example, since boot code is updated infrequently in PC BIOS applications,  $V_{PP}$  may be held at ground for standard operation. Implementation of the above logic controlled circuit would allow in-system code updates, while protecting code during normal operation.

Table 2. Advantages of Each VPP Circuit

| Characteristic                | 12V Circuit |

|-------------------------------|-------------|

| Lowest Cost/Fewest Components | Figure 5    |

| Least Current/Most Reliable   | Figure 4    |

### NOTES:

A DC/DC converter shutdown input may be the best solution if available.

5V solution is reliable and requires very low operation current.

The commercial temp 28F200/002BX and 28F400/004BX components offer a 12V ±10% tolerance at a reduced cycling specification.

### 3.1 V<sub>PP</sub> Solution: Implementing a Lockall# Input

As discussed, existing internal write protection circuits can be used by system designers to gain additional write control when required. A signal called Lockall#, generated by a general purpose I/O output, could prevent all write and erase commands when asserted. Several circuits designed to accomplish this are discussed below.

### 3.1.1 5V/12V LOCKALL# DC-DC CONVERTER SOLUTION

Many designs use a DC-DC converter to supply 12V to  $V_{PP}$ . Since most DC-DC converters have a Shutdown pin, Lockall# can be connected directly to this converter input, saving design time and production costs.

Should the DC-DC converter in use not have a Shutdown control input, a circuit connected externally to the converter can be used to regulate input voltage. Such a solution would require the use of a BJT to control the input to the voltage converter.

While a DC-DC converter solution offers the most costeffective method to control  $V_{PP}$ , it is only an option when the converter provides power exclusively to the flash device.

### 3.1.2 5V LOCKALL# MOSFET SOLUTION

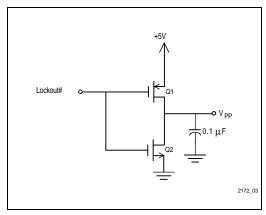

A two MOSFET configuration may be used to control the input voltage to  $V_{PP}$ , as shown in Figure 3.

The source of a p-channel, enhancement mode MOSFET is connected to the power source. The gate and drain are connected to Lockall# and  $V_{PP}$ , respectively. Operation of this circuit may be summarized as follows: a 0V Lockall# drops  $V_{PP}$  to 0V and a +5V Lockall# raises  $V_{PP}$  to +5V.

Table 3. 5V/12V VPP Lockall# Circuit Truth Table

| Lockall# | Q1  | Q2  | Q3  | V <sub>PP</sub>      |  |

|----------|-----|-----|-----|----------------------|--|

| Low      | Off | On  | Off | 0V                   |  |

| High     | On  | Off | On  | ~V <sub>SOURCE</sub> |  |

Figure 3. This SmartVoltage Circuit Will Prevent Program and Erases When Lockall# Is Asserted

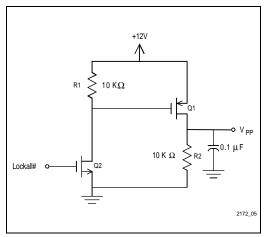

### 3.1.3 12V LOCKALL# MOSFET SOLUTION

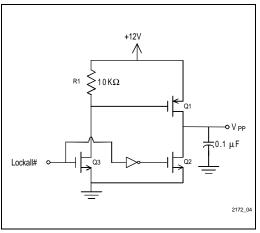

Another method of implementing a Lockall# control is shown in Figure 4. A p-channel enhancement mode MOSFET, Q1, is used to transfer 12V from its source to its drain,  $V_{PP}$ . When Lockall# is asserted, Q3 turns on causing a current across R1. The resulting voltage drop at the gate of Q1 causes Q1 to turn on, delivering 12V to  $V_{PP}$ , minus a small voltage drop across Q1. Table 3 shows the truth table of operation.

Figure 4. This Circuit Offers Reliable Lockall# Protection in a 12V V<sub>PP</sub> System

### 3.1.4 12V LOCKALL# MOSFET WITH RESISTOR SOLUTION

The cost of the circuit, discussed in Section 3.1.3, may be reduced by removing the inverter and replacing one of the n-channel MOSFETs with a resistor as shown in Figure 5. The resistor, R2, will increase the amount of current drawn through Q1. To calculate this additional current use Ohm's Law. If V<sub>PP</sub> equals 12.0V, then:

$$12.0V = i \times 10 \text{ K}\Omega$$

Solving for i yields 1.2 mA. Ensure that the power source can meet the maximum current demand of flash plus the current through the resistor.

Figure 5. Although This Circuit Will Cost Less to Implement, It Requires More Current Than Other Solutions

### 4.0 P-CHANNEL ENHANCEMENT MODE MOSFET SELECTION

Selection of the P-Channel MOSFET is critical to proper operation. For a listing of potential vendors, refer to Table 4. If a different device is used, ensure that V<sub>PP</sub> tolerances and other specifications are met.

Two main characteristics must be taken into account when choosing the p-channel enhancement mode MOSFET: price and performance. Since  $V_{PP}$  must not drop below 11.4V for 12V  $V_{PP}$ , or 4.5V for 5V  $V_{PP}$ , the transistor must guarantee a relatively low  $V_{DS}$  voltage drop when on. Because the price of the transistor may be directly related to this voltage drop, specified by the resistance  $r_{DS}$ , choose the largest  $r_{DS}$  allowable within the power supply tolerance.

For example, if a 12V flash device obtains power from a DC-DC converter with a 3% output tolerance, the maximum voltage drop across the transistor should be no more than 0.24V. This may be calculated by taking 3% of 12V, then subtracting the result from the maximum allowable voltage drop of 5% of 12V, or 0.6V.

$$12V \times 5\% = 0.6V$$

$$12V \times 3\% = 0.36V$$

$$0.6V - 0.36V = 0.24V$$

$r_{DS}$  may now be calculated using Ohm's Law. Assuming a maximum current of 30 mA during a write cycle,  $r_{DS}=8\Omega.$

$$0.24V = 30 \text{ mA} \times r_{DS}$$

Thus a device with  $r_{DS}$  less than  $8\Omega$  should be selected.

| Source    | Part Number  | r <sub>DS</sub> (Max) | Test                                             | Package              | Cost  |

|-----------|--------------|-----------------------|--------------------------------------------------|----------------------|-------|

| Cource    | 1 art Humber | TDS (Max)             | Condition                                        | 1 ackage             | 0031  |

| Toshiba   | 2SJ148       | 2 Ω                   | I <sub>D</sub> = 50 mA<br>V <sub>GS</sub> = 10V  | TO-92                | \$.90 |

| Toshiba   | 2SJ168       | 2 Ω                   | $I_D = 50 \text{ mA}$<br>$V_{GS} = 10 \text{V}$  | 2-3F1F               | 1.05  |

| Harris    | RFD10P03L    | 0.2 Ω                 | I <sub>D</sub> = 10 A<br>V <sub>GS</sub> = 5V    | TO-252AA<br>TO-251AA | 64    |

| Siliconix | Si9405DY     | 0.1 Ω                 | I <sub>D</sub> = 2 A<br>V <sub>GS</sub> = 10V    | SO-8                 | 1.30  |

| Micrel    | MiV94030BM4  | 1 Ω                   | I <sub>D</sub> = 100 mA<br>V <sub>GS</sub> = 10V | SOT-143              | .58   |

Table 4. P-Channel Enhancement MOSFET Possible Vendor List

Cost estimates based on published 10K unit pricing at the time this application note was written.

## 5.0 RP# AND WP# CHARACTERISTICS

RP# controls three different functions: reset, deep powerdown, and boot block unlocking. When RP# equals  $V_{\rm IL}$ , the device is in reset and deep power-down mode. In this mode, the device's outputs are in a high impedance state, the Write State Machine is reset, and the device draws minimum current. Furthermore, all write and erase commands are ignored, providing another means of data protection during power-up and power-down. The device requires a minimum access time  $t_{\rm PHQV}$  to access valid data. For a more complete discussion of reset timing, flash  $t_{\rm PHQV}$  times, and Intel microcontroller reset timings, refer to Section 6.0 and Appendix B.

During normal read/write operation RP# will be set to  $V_{IH}$ . At this voltage, the boot block, in Intel's boot block products, remains locked to writes and erases. However, all commands to other blocks return valid results. For Intel's FlashFile products, all blocks are unlocked to writes.

For Intel's boot block flash products, when RP# equals  $V_{HH}$ , the boot block becomes unlocked and may be written to or erased. This state overrides any control from the WP# input.

The WP# control pin, which was introduced on SmartVoltage parts, locks and unlocks the boot block, on boot block products, much like RP#. Since many applications which use SmartVoltage will not have access to a 12V source, WP# provides control of boot block locking and unlocking with a logic-level signal.

The state of WP# is only relevant when RP# equals  $V_{IH}$ . When WP# equals  $V_{IH}$ , the boot block is unlocked. Deasserting WP# to  $V_{IL}$  locks the boot block. However, when RP# equals  $V_{HH}$ , the boot block will unlock, regardless of the assertion level of WP#. Refer to Table 5 for a complete truth table of WP# and RP#.

Table 5. Write Protection Truth Table for SmartVoltage Boot Block Family

| Write Protection<br>Provided | Operating Mode        | V <sub>PP</sub>     | RP#             | WP#             |

|------------------------------|-----------------------|---------------------|-----------------|-----------------|

| Lock All Blocks              | Read Only             | V <sub>IL</sub>     | Х               | Х               |

| Reset/All Blocks Locked      | Reset/Deep Power-Down | ≥ V <sub>PPLK</sub> | $V_{IL}$        | Х               |

| Unlock All Blocks            | Standard Operation    | ≥ V <sub>PPLK</sub> | V <sub>HH</sub> | Х               |

| Lock Boot Block              | Standard Operation    | ≥ V <sub>PPLK</sub> | V <sub>IH</sub> | V <sub>IL</sub> |

| Unlock All Blocks            | Standard Operation    | ≥ V <sub>PPLK</sub> | V <sub>IH</sub> | $V_{IH}$        |

Table 6. Advantages of Each RP# Circuit

| Characteristic                          | RP#      |

|-----------------------------------------|----------|

| Lowest Cost/Fewest Parts, Most Reliable | Figure 7 |

| Hands-Off In-System Updates             | Figure 6 |

### NOTE:

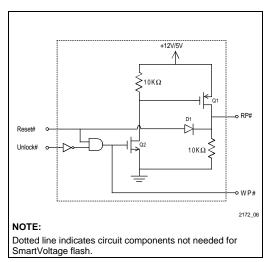

For SmartVoltage devices, Unlock# and Reset# inputs connect directly to RP# and WP#.

### 5.1 RP# and WP# Solutions: Implementing a Reset# and Unlock# Input

In some applications, the system design may require the functionality of both a lock and reset signal. For SmartVoltage products, reset and lock inputs can be tied directly to RP# and WP# respectively. However, for flash products without WP#, optional circuits may be needed. Several circuits, which provide this level of control, will be discussed in the following sections.

### 5.1.1 RP# MOSFET SOLUTION

The circuit in Figure 6 shows a two MOSFET configuration that switches voltage between 0, +5, and +12V. The design accommodates SmartVoltage applications using either +12V or +5V. Layouts currently using a non-SmartVoltage product, but planning to convert to SmartVoltage, may implement this circuit as shown including WP#. Thus to upgrade, no modification of the design or layout will be required to support SmartVoltage products. SmartVoltage designs may connect Reset# and Unlock# inputs directly to RP# and WP#.

The operation of this circuit is summarized in Table 7.

Table 7. Reset# and Unlock# Circuit Truth Table

| Reset# | Unlock# | Q1  | Q2                    | RP# | WP# |

|--------|---------|-----|-----------------------|-----|-----|

| Low    | Low     | Off | Off                   | 0V  | 0V  |

| Low    | High    | Off | Off                   | 0V  | 0V  |

| High   | Low     | On  | n On ~V <sub>PP</sub> |     | 5V  |

| High   | High    | Off | Off                   | 5V  | 0V  |

Figure 6. Implement Reset# and Unlock# Inputs

Using this Circuit for Hands-Off Boot Block

Updating

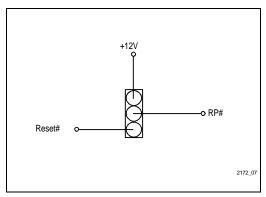

### 5.1.2 RP# JUMPER SOLUTION

For applications with infrequent boot code updates, a jumper circuit is an option. This solution greatly reduces the cost of implementation, but also reduces the convenience of in-system updating. An example jumper configuration may be seen in Figure 7. In this configuration, the jumper connects RP# to the reset signal during normal operation and is switched to pull RP# up to 12V when the boot block needs to be reprogrammed.

Figure 7. Implementing Unlock# and Reset#

Inputs Using a Jumper Reduces Cost, but Also

Decreases Convenience

## 6.0 INTEL MICROCONTROLLER AND MICROPROCESSOR RESET TIMING CONSIDERATIONS

Every processor family available has a unique reset process and requires a different amount of time to execute the first instruction fetch. When interfacing memory to a processor, several factors should be examined.

One such consideration which must be addressed is the location of boot code, since loading the boot code is generally part of the reset process. If the processor does not have internal memory, it must access the boot code through an external memory bus. Thus, the memory devices must have already returned from the reset state by the time the CPU fetches data from the memory bus. In many systems, RP# and the CPU's RESET# are tied together. If the memory unit becomes available after the controller expects data, a solution must be devised to hold the CPU's request for data until memory is fully reset.

### 6.1 CPU Reset and RP# Timing

For flash applications, the processor's reset line may be tied to RP#. Thus, the system and CPU are in reset when RP# is at  $V_{\rm IL}$ . To determine if the flash device will return from reset in time to meet the processor's request for boot code, the  $t_{\rm PHQV}$  specification must be examined. Since  $t_{\rm PHQV}$  includes flash access time, the processor may latch data off the memory bus after this time has elapsed.

To illustrate reset timings, consider a 25 MHz 80C196NP, which may execute its first instruction fetch as early as 120 ns after reset. Since tpHQV for the 28F200BV-80 is specified at 450 ns, a RESET# delay would be required. However, no delay would be required for a 33 MHz Intel386<sup>TM</sup> embedded processor since the first instruction fetch would occur 510 ns after reset.

Table 8, in Appendix B, lists the specifications for the deassertion of reset to data valid for several Intel microprocessors and microcontrollers.

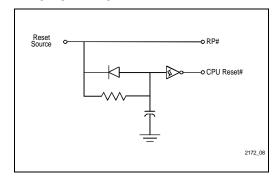

### 6.2 CPU Reset Delay Techniques

Because some CPUs return from reset faster than memory, a method must be employed to delay the processor reset. To prevent the processor from fetching erroneous data, an RC network may be inserted between the reset line and the reset pin of the processor. One such circuit is shown in Figure 8.

The Reset Source input could represent a number of signals. For example, a PowerGood signal or user-initiated reset may be connected to this input. The resistor and capacitor should be chosen to create a long enough delay to ensure flash resets. To ensure a rapid trigger from the reset voltage to normal operating voltage, a Schmitt-Trigger should be used, keeping in mind the assertion level of the processor's Reset# input. Finally, a diode in parallel with the resistor allows a quick discharge of CPU Reset# when switching from a voltage high to voltage low.

Figure 8. If a Microcontroller Attempts to Fetch Code before Memory Resets, a Delay Circuit Such As This One Should be Added

To calculate the resistor and capacitor values, use the equation:

$$V_C(t) = V_S + (V_0 - V_S)e^{-t/RC}$$

For example, if an Intel 80C196NP microcontroller running at 25 MHz interfaces with a 28F400BX, a minimum delay of 180 ns must be inserted to ensure valid data upon reset or power-up. If the Schmitt-Trigger switches voltage, from logic low to logic high, at  $V_{T+} = 0.6 V$  and the source voltage  $V_{\rm S} = 5 V$  then the equation becomes:

$$0.6V=5V-5Ve^{\text{-}180/RC}$$

Solving for RC yields  $1.41 \times 10^{-6}$ . The resistance and capacitance may then be chosen accordingly. Since this equation yields the minimum RC requirement, this value may be adjusted for guardband.

### 7.0 SUMMARY

The various control and power inputs of Intel's Flash memory are highly versatile. These control signals have circuitry on-chip which prevent unintentional writes to the device and may also be used for additional levels of protection. Several optional circuits were presented in this application note which would give the system design an additional level of protection against unwanted writes.

### 8.0 ADDITIONAL INFORMATION

### 8.1 References

| Order Number | Document                                          |  |  |  |  |  |

|--------------|---------------------------------------------------|--|--|--|--|--|

| 297372       | 16-Mbit Flash Product Family User's Manual        |  |  |  |  |  |

| 292092       | AP-357, "Power Supply Solutions for Flash Memory" |  |  |  |  |  |

### 8.2 Revision History

| Number | Description      |

|--------|------------------|

| -001   | Original Version |

## APPENDIX A BOOT BLOCK AND FlashFile ARCHITECTURE

Intel Flash offers two blocking architectures to address the needs of today's applications. FlashFile architecture divides memory into 64-KB blocks, while the boot block architecture divides memory asymmetrically into differing sized blocks and allows one of these blocks to be locked. This lockable block, called the boot block, can only be written when specific control pins are asserted.

### **Boot Block Architecture**

The boot block flash architecture was designed for applications which require in-system updates, but have critical code which must be protected. For example, PC BIOS may require in-system updates, however, the boot code requires additional protection since the system cannot boot-up if this code becomes corrupted.

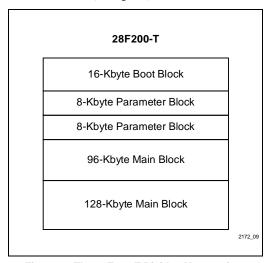

Intel offers boot block architectures with the boot block on the bottom or at the top of the memory array. The 28F200-T is an example of the top architecture. Memory is divided into five blocks with the 16-KB boot block residing at the top of the memory array. Next, two 8-KB parameter blocks, a 96-KB main block, and a 128-KB main block follow (see Figure 9).

Figure 9. The 28F200-T Divides Memory into Asymmetrical Blocks and Allows the Boot Block to Be Locked

### FlashFile Architecture

Other applications require a more symmetric approach to memory. The FlashFile architecture organizes the memory array into equally sized blocks. For example, the 28F008SA, shown in Figure 10, has sixteen separately erasable 64-KB blocks. This architecture allows disk emulation as well as in-system updateability for embedded applications.

Figure 10. The 28F008SA Has Sixteen Seperately Eraseable Blocks

## APPENDIX B RESET CONSIDERATIONS

Table 8. Reset to First Data Latch

|                                    | No. of<br>CLK<br>Cycles | 12 MHz<br>(ns) | 16 MHz<br>(ns) | 20 MHz<br>(ns) | 24 MHz<br>(ns) | 25 MHz<br>(ns) | 33 MHz<br>(ns) | 40 MHz<br>(ns) | 50 MHz<br>(ns) | 66 MHz<br>(ns) |

|------------------------------------|-------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| i486™ SX<br>IntelDX2™<br>Processor | 217                     |                |                |                |                |                | 6510           |                | 4340           | 3255           |

| i386™ EX<br>Processor              | 350                     |                | 21875          | 17500          |                | 14000          | 10500          |                |                |                |

| 80186                              | 14                      | 1167           |                | 700            |                | 560            |                | 350            |                |                |

| i960®<br>Processor                 | 32                      |                | 2013           | 1600           |                | 1280           | 960            |                |                |                |

| MCS® 96<br>Controller              | 3                       | 249            | 189            | 150            |                | 120            |                |                |                |                |

| MCS® 251<br>Controller             | 34                      | 2833           | 2125           |                |                |                |                |                |                |                |

| MCS® 51<br>Controller              | 24                      | 2000           | 1500           | 1200           | 1000           |                |                |                |                |                |

### NOTES:

Timings provided for all available speeds at time of publication (no speeds in shaded areas).

Specifications are provided for comparison only. Consult datasheets for current timing specifications.

## APPENDIX C POTENTIAL SOURCES FOR P-CHANNEL MOSFET DEVICES

### **Toshiba Semiconductor**

Toshiba offers one of the smallest surface mount MOSFETs available. The 2-3F1F package occupies a space of 2.5 mm x 2.9 mm and is ideal for mobile applications. Toshiba also offers a JEDEC standard TO-220 through-hole package.

### **United States:**

9775 Toledo Way Irvine, California 92718 Tel: (714) 455-2000 Fax: (714) 859-3963

### Europe:

Hansallee 181 D-40549 Düsseldorf, Germany Tel: 0211-52960 Fax: 0211-5296400

#### Asia:

10F Lippo Sun Plaza 28 Canton Road Tsim Sha Tsui Kowloon, Hong Kong Tel: 37 56 111 Fax: 37 50 969

### **Harris Semiconductor**

Harris offers many low  $r_{DS}$ , p-channel power MOSFETs. The RFD10P03L is a competitively-priced power MOSFET that is available in both a through-hole and surface mount package.

#### **United States:**

1301 Woody Burke Road Melbourne, Florida 32901 Tel: (407) 724-7000

### **Europe:**

Mercure Center 100 Rue de la Fusee 1130 Brussels, Belgium Tel: 32 2 246 21 11 Fax: 32 2 246 22 05/ ...09

#### Asia

Shinjuku NS Bldg. Box 6153 2-4-1 Nishi-Shinjuku Shinjuku-Ku, Tokyo 163-08 Japan Tel: (81) 03-3345-8911 Fax: (81) 03-3345-8910

### Siliconix (TEMIC)

Siliconix offers one of the lowest  $r_{DS}$  logic level PFETs available. The S08 package is part of the "Little Foot" series and is an 8-pin surface mount package.

#### **United States:**

2201 Laurelwood Road P.O. Box 54951 Santa Clara, CA 95056-9951 Tel: (408) 988-8000 Fax: (408) 727-5414

### **Europe:**

TEMIC Telefunken Microelectonic GmbH Theresienstrasse2 74072 Heilbronn, Germany Tel: 49 7131 67-0 Fax: 49 7131 67-2340

### Asia:

TEMIC Microsystems Hong Kong, Ltd. Suite 1701 World Finance Center South Tower, Harbour City 17 Canton Road, Tsishatsui Kowloon, Hong Kong Tel: 852 23 789 789 Fax: 852 23 755 733

### Silconix, cont.

TEMIC (S) Pte. Ltd. AEG Building #02-00 25 Tampines Street 92 Singapore 1853 Republic of Singapore Tel: 65 788 6668 Fax: 65 788 3383

### **Micrel Incorporated**

Micrel offers both a small package and low-cost p-channel enhancement MOSFET. The SOT-143 package is a 4-terminal surface mount device.

Micrel, Inc. 1849 Fortune Drive San Jose, CA 95131 Tel: (408) 944-0800 Fax: (408) 944-0970

### NOTE:

This list is intended for reference only and in no way represents all companies that produce p-channel enhancement mode MOSFETs. Since this industry develops many new products each year, Intel recommends that the designer contact the vendors for the latest products. Intel Corporation assumes no responsibilities for circuitry other than circuitry embodied in Intel products. No other circuit patent licenses are implied.

Filename: 292172\_1.DOC

Directory: C:\TESTDOCS\SUBMIT

C:\WINDOWS\WINWORD6\TEMPLATE\ZAN\_\_\_\_1.DOT Template:

Title: E Subject:

Mary Ann Hooker Author:

Keywords:

Comments:

Creation Date: 09/05/95 10:33 AM

Revision Number:

Last Saved On: 11/10/95 3:11 PM Last Saved By: Mary Ann Hooker Total Editing Time: Last Printed On: 103 Minutes 01/30/96 10:43 AM

14

As of Last Complete Printing

Number of Pages:

Number of Words: 3,933 (approx.) Number of Characters: 22,419 (approx.)