### **AP-380**

# APPLICATION NOTE

# Upgrading System Designs from Bulk Erase to Boot Block Flash Memories

BRIAN DIPERT SENIOR TECHNICAL MARKETING ENGINEER

August 1996

Order Number: 292129-002

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

\*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION 1996

CG-041493

### **CONTENTS**

| PAGE                                          | PAGE                                                              |

|-----------------------------------------------|-------------------------------------------------------------------|

| 1.0 INTRODUCTION5                             | APPENDIX A  DIP Pinout Comparison10                               |

| 2.0 PINOUT COMPATIBILITY5                     |                                                                   |

| 2.1 Reset/Power-Down Pin (RP#)5               | APPENDIX B                                                        |

| 2.2 Controlling RP#6                          | PLCC Pinout Comparison11                                          |

| 2.3 Pinout Adaptability (28F010 to 28F001BX)6 | APPENDIX C                                                        |

| 2.4 Pinout Adaptability (Other Densities) 6   | TSOP (Standard) Pinout Comparison12                               |

| 3.0 MEMORY MAP COMPATIBILITY6                 | APPENDIX D                                                        |

| 4.0 PROGRAM AND ERASE ALGORITHM               | Bulk Erase Flash Memory Program Algorithm . 13                    |

| COMPATIBILITY8                                | APPENDIX E                                                        |

| 5.0 DC SPECIFICATION COMPATIBILITY8           | Bulk Erase Flash Memory Erase Algorithm 14                        |

| 5.1 Current Draw during Reads9                | , ,                                                               |

| 5.2 Current Draw during Program/Erase9        | APPENDIX F                                                        |

| 6.0 AC READ SPECIFICATION                     | Boot Block Flash Memory Automated Program Algorithm15             |

| COMPATIBILITY9                                | -                                                                 |

| 7.0 AC WRITE SPECIFICATION                    | APPENDIX G                                                        |

| COMPATIBILITY9                                | Boot Block Flash Memory Automated Erase Algorithm16               |

| 8.0 SUMMARY9                                  | APPENDIX H                                                        |

|                                               | Boot Block Flash Memory Status Register17                         |

|                                               | APPENDIX I                                                        |

|                                               | DC Specification Comparison18                                     |

|                                               | APPENDIX J                                                        |

|                                               | AC Read Specification Comparison19                                |

|                                               | APPENDIX K                                                        |

|                                               | AC Write Specification Comparison20                               |

|                                               | APPENDIX L                                                        |

|                                               | Intel Bulk Erase and Boot Block Flash Memory Related Datasheets21 |

#### **REVISION HISTORY**

| Nu | ımber | Description                                                                     |

|----|-------|---------------------------------------------------------------------------------|

| -  | 001   | Original version                                                                |

| -  | 002   | Updated program/erase algorithms Textual corrections and other cosmetic changes |

#### 1.0 INTRODUCTION

Boot Block flash memories from Intel Corporation ensure safe and simple embedded code updates for system designs. The optimized blocking of these devices locks and protects key kernel boot software while enabling easy upgrade of the majority of system code and integrating ROM, bulk flash memory and EEPROM/NVRAM functionality in one solution. Automated algorithms simplify update routines and extend system flexibility.

This application note assists in upgrading existing system designs based on first-generation bulk erase flash memories to Intel's Boot Block devices. Table 1 shows a summary list of both bulk erase and Boot Block flash memories.

Table 1. Intel Bulk Erase and Boot Block Flash Memories

| Bulk Erase                                        | Boot Block                                                |

|---------------------------------------------------|-----------------------------------------------------------|

| 28F256A<br>(x8, 256 Kb)<br>32-pin DIP, PLCC       | 28F001BX<br>(x8, 1 Mb)<br>32-pin DIP, PLCC,<br>TSOP       |

| 28F512<br>(x8, 512 Kb)<br>32-pin DIP, PLCC        | 28F002BX<br>(x8, 2 Mb)<br>40-pin TSOP                     |

| 28F010<br>(x8, 1 Mb)<br>32-pin DIP, PLCC,<br>TSOP | 28F200BX<br>(x8/x16, 2 Mb)<br>44-pin PSOP,<br>56-pin TSOP |

| 28F020<br>(x8, 2 Mb)<br>32-pin DIP, PLCC,<br>TSOP | 28F004BX<br>(x8, 4 Mb)<br>40-pin TSOP                     |

|                                                   | 28F400BX<br>(x8/x16, 4 Mb)<br>44-pin PSOP,<br>56-pin TSOP |

Throughout this document, specific examples highlight conversion of a 28F010-based design to the 28F001BX. However, the techniques shown are, in general, applicable for any bulk erase-to-Boot Block conversion. Device datasheets (listed in Appendix L) provide comprehensive pinouts, specifications, etc. for all bulk erase and Boot Block flash memories. Issues specific to conversion other than 28F010 to 28F001BX will be spelled out where appropriate.

This application note covers the following sections:

- · Pinout Compatibility

- Memory Map Compatibility

- Program and Erase Algorithm Compatibility

- · DC Specification Compatibility

- AC Read Specification Compatibility

- AC Write Specification Compatibility

For additional assistance in converting your designs to Boot Block flash memories, please contact your local Intel or distribution technical sales representative.

#### 2.0 PINOUT COMPATIBILITY

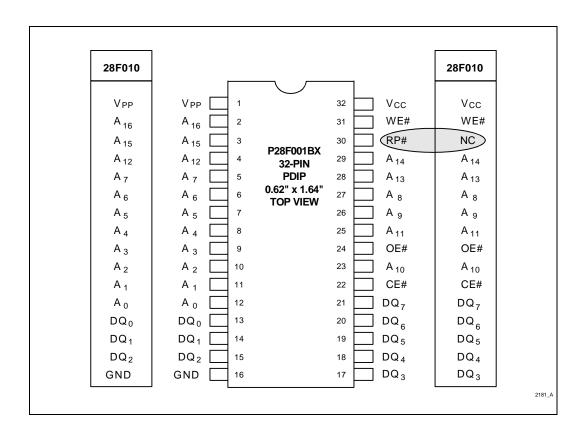

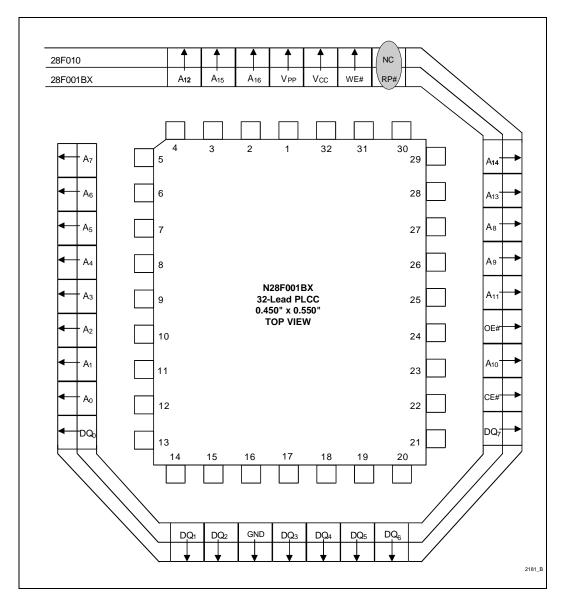

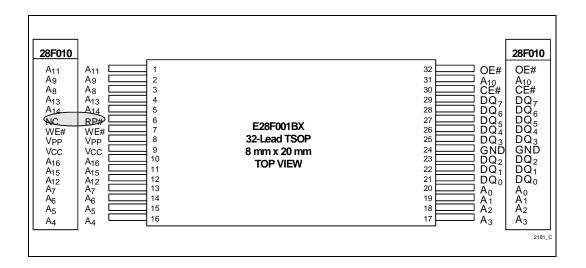

Appendices A, B and C show pinout comparisons between the 28F010 and 28F001BX flash memories. In this section, we'll discuss two key aspects of pinout compatibility:

- Added pins and functions with Boot Block devices (i.e., the RP# pin)

- Pinout adaptability between bulk erase and Boot Block memories at equivalent densities.

#### 2.1 Reset/Power-Down Pin (RP#)

Compared to bulk erase flash memory alternatives, Boot Block flash memories add a multi-function input called RP# (previously known as PWD#, renamed for JEDEC standardization compatibility). RP# acts as a "master on/off switch" for the flash memory, disabling a majority of internal circuitry and putting the device in an ultra-low power consumption mode when active. RP# has several distinct applications in system designs:

- It transitions the Boot Block flash memory to deep power-down mode—ideal for lowest power consumption when the memory is not being accessed for an extended period. In this application, RP# is toggled by a general purpose CMOS I/O line controlled by system power management software.

- It fully protects the flash memory from unwanted command writes during system power transitions.

In this application, RP# is controlled by the power supply POWERGOOD output, or by discrete analog voltage monitoring circuitry.

It resets all internal automation within the flash memory and transitions the device to the default read array mode. In this application, RP# is controlled by the same RESET# signal that resets the system CPU.

RP# also "unlocks" the boot block (see Section 3 for details), allowing block erase and location programming, when 12V is applied to the pin.

#### 2.2 Controlling RP#

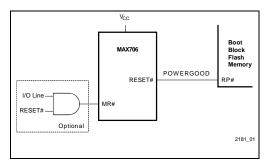

The minimum recommended RP# control that should be implemented in Boot Block flash memory designs is shown in Figure 1. In this configuration, RP# is connected to the system power supply POWERGOOD output, or to the output of analog voltage monitoring circuitry such as the MAX70x series from Maxim Integrated Products. Additional information on flash memory write protection techniques can be found in application note AP-374, "Implementing Reliable Flash Memory Interfaces" (order number 292123).

Figure 1. RP# Control

MAX70x devices (and functional equivalents from other manufacturers) also provide a MR# (manual reset) input that toggles POWERGOOD—not only when the supply voltage is out-of-spec, but also when MR# is active. Connecting MR# to system RESET#, therefore, allows successful CPU reboot of the flash memory, even if reset occurs during program or erase operations. RP# active transitions terminate flash memory automation and return the device to read array mode.

If deep power-down mode is also implemented, the MR# input to the MAX70x becomes the logical "AND" of system reset and control logic such as a system I/O line. Toggling the I/O line "low" puts the flash memory in deep power-down mode.

In the majority of applications, kernel code stored in the boot block is programmed before the flash memory is installed on the system board. Kernel code is fully protected from alteration by providing no subsequent 12V capability on RP#. However, if future Boot Block update is desired, a switchable or jumpered 12V on this pin can be implemented.

# 2.3 Pinout Adaptability (28F010 to 28F001BX)

As Appendices A, B and C show, the package pinouts for the 28F010 and 28F001BX are very similar. The 28F010's NC (no connect) pin, reserved for address  $A_{17}$  on the 28F020, becomes RP# on the 28F001BX. Minor logic modification adds RP# control described in the previous section of this application note.

# 2.4 Pinout Adaptability (Other Densities)

Since the 28F256AS and 28F512 are already pinout-compatible with the 28F010, upgrades from these bulk erase flash memories to the 28F001BX are relatively straightforward. No-connects on the 28F256A and 28F512 become addresses for the higher-density 28F001BX.

Pinout conversion from the 2-Mbit 28F020 to the 28F002BX/200BX or 28F004BX/400BX is not quite as intuitive and probably requires a board re-layout. Appendices A, B and C indicate that the 28F001BX uses all 32 pins in DIP, PLCC and TSOP. Higher density Boot Block flash memories, therefore, come in higher pincount packages (see Table 1), both to handle the x16 data bus and BYTE# control of the 28F200BX and 28F400BX.

#### 3.0 MEMORY MAP COMPATIBILITY

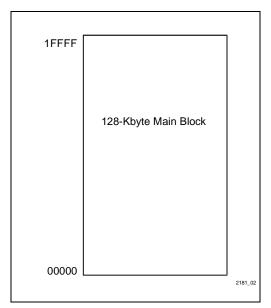

As their names imply, bulk erase flash memories erase all locations within the flash memory map at the same time. An example memory map for the 28F010 is shown in Figure 2.

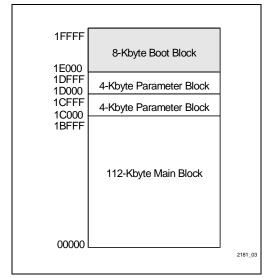

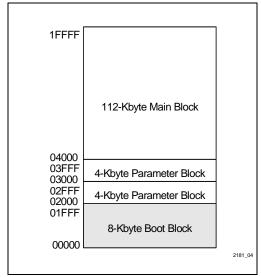

Boot Block flash memories, on the other hand, have separately-erasable boot, parameter and main blocks. Additionally, "top" and "bottom" versions of all Boot Block devices provide boot block locations compatible with a wide range of microprocessors and embedded processors (explained in Table 2). Figures 3 and 4 show memory maps for the 28F001BX-T ("top") and 28F001BX-B ("bottom"), respectively.

Figure 2. 28F010 Memory Map

Table 2. Boot Block Flash Memory Microprocessor/Microcontroller Compatibility Chart

| 28F00xBX-T or<br>28Fx00BX-T         | 28F00xBX-B or<br>28Fx00BX-B                           |

|-------------------------------------|-------------------------------------------------------|

| 8086/8088                           | i960® KA/KB<br>Microprocessors                        |

| 80C186/80C188<br>and proliferations | i960 SA/SB<br>Microprocessors                         |

| 80286                               | MCS®-51<br>Microcontroller Family                     |

| i386™<br>Microprocessor Family      | MCS-96<br>Microcontroller Family                      |

| i486™<br>Microprocessor Family      | AMD 29K Family                                        |

| Pentium®<br>Microprocessor          | Most Motorola<br>Microcontrollers/<br>Microprocessors |

| i860®<br>Microprocesser Family      |                                                       |

| i960 CA/CF<br>Microprocessor        |                                                       |

As first mentioned in Section 2, the boot block is intended to contain secure code which minimally will bring up the system and download code to the other blocks, if required. Once programmed, hardware-locking the boot block from further alteration guarantees true system protection.

Figure 3. 28F001BX-T Memory Map

Figure 4. 28F001BX-B Memory Map

The main block(s), on the other hand, store the majority of the system code and are easily updated, since they are not hardware-lockable. Parameter blocks are intended to replace EEPROM and battery-backed SRAM for parameter storage in many designs, but these smaller blocks can also be used to store updateable system code, if desired.

Re-segmenting your system software will allow you to take full advantage of the Boot Block architecture. The contents of "kernel" code stored in the boot block vary from system to system and application to application, but the guidelines that follow apply in most cases. The core boot code should perform some, if not all, of the following functions:

- Minimally initialize the system (configure the processor, chipset, floppy drive to allow reading in of the update code, etc.).

- Perform a "checksum" of the remainder of the flash memory data.

- If checksum verifies correctly, jump to the main portion of the boot code, found in another block of the device.

- If checksum fails (meaning that one or several of the other flash memory blocks contain invalid code/data):

- Alert the user through speaker beep, message on display, LED flash, etc.

- Erase all other blocks of the flash memory. This means that the boot block must store the program and erase algorithms for the flash memory.

- Download new data from floppy disk, external connector, etc., and reprogram the other blocks.

- Reboot the system.

# 4.0 PROGRAM AND ERASE ALGORITHM COMPATIBILITY

Boot Block flash memories include second-generation automated program and erase algorithms (shown in Appendices F and G) that enhance the flash memory interface and overcome shortcomings of bulk erase flash memory "manual" counterparts (Appendices D and E).

Boot Block algorithms are fully automated after system software issues program or erase command sequences and include automated verify. An internal oscillator measures all timing delays, onchip counters increment through addresses and keep track of the erase and program pulses. Preprogramming of the selected block is automatically done before erasing the block. Flash memory automation allows the system to perform other functions during program and erase operations. Automation also greatly simplifies read/program/erase of multiple flash memories in parallel.

Enhanced interfacing includes a Status Register in the flash memory (shown in Appendix H) that informs the system as to the progress and success/failure of the internal automation. Integrated circuitry monitors the status of the V<sub>PP</sub> voltage throughout program or erase, terminating the algorithm if it detects that V<sub>PP</sub> has fallen out of tolerance and relaying this information back to the system via the status register.

Although automated Boot Block flash memory Program and Erase commands are essentially backwards-compatible with those used for bulk erase flash memories, the Boot Block flash memory automated algorithms themselves (although simpler) are incompatible with bulk erase manual counterparts. Compare Appendices D and F (program), and E and G (erase), to see the different algorithm steps. High-level "C" and assembly language software drivers, available for all Boot Block flash memories, simplify algorithm development (contact your local Intel or distribution sales office).

# 5.0 DC SPECIFICATION COMPATIBILITY

Boot Block and bulk erase flash memories are all CMOS devices with TTL-compatible input buffers. They all require 12V  $V_{PP}$  for program and erase, and all have  $V_{LKO}$  circuitry to protect the flash memory from unintended command writes during system power transitions.

Bulk erase and Boot Block flash memories have identical CMOS current draw specifications in standby mode. Boot Block flash memories add the deep power-down mode, not found in bulk erase devices, for lowest power consumption. Versions of 2-/4-Mbit Boot Block flash memories can also be operated at 3.3V  $V_{\rm CC}$ , for lower power consumption in all operating modes (compared to 5V  $V_{\rm CC}$  equivalent devices).

Specific DC specification differences between the 28F010 and 28F001BX are shown in Appendix I. Current draw comparison trends for bulk erase and Boot Block flash memories are described in the following sections. For particular specifications on devices other than the 28F010 and 28F001BX, consult device datasheets (listed in Appendix L).

#### 5.1 Current Draw during Reads

The 28F001BX has identical  $V_{CC}$  and  $V_{PP}$  read current specifications to bulk erase flash memories. 2-/4-Mbit Boot Block flash memories have higher  $V_{CC}$  current specifications, reflective of their faster access times (see Section 6.0) and x16 data buses. However, due to their automatic power savings feature, these devices will be generally compatible with bulk erase flash memories when similarly configured (x8), and operated at the same read frequencies.

#### 5.2 Current Draw during Program/Erase

Boot Block flash memories will tend to consume more current through  $V_{\rm CC}$  during program/erase compared to bulk erase devices, due to the automation running within them. Specifically, the 28F001BX maximum  $V_{\rm CC}$  current specification during program/erase is 20 mA, while that for the 28F010 is 15 mA. 2-/4-Mbit Boot Block flash memory current draw is higher.

Vpp current draw during program/erase is identical for the 28F001BX, 2-/4-Mbit Boot Block flash memories (during byte programming) and all bulk erase flash memories. The 2-/4-Mbit Boot Block devices, when executing 16-bit programming, draw additional Vpp current.

# 6.0 AC READ SPECIFICATION COMPATIBILITY

Boot Block flash memory read timing specifications are identical (or superior) to bulk erase devices at equivalent speed bins. Boot Block devices add an additional timing specification, t<sub>PHQV</sub>, that defines "wakeup" delay from RP# high to valid data. AC read specifications for the 28F010 and 28F001BX are found in Appendix J.

Design "shrinks" of the 28F010, 28F020 and 28F001BX have moved these products to a sub-micron manufacturing process. These redesigns allow Intel to offer faster speed bins for these devices. Intel has maintained compatible read specifications for all existing and future versions of the 28F001BX and 28F010/28F020. Contact you local Intel or distribution sales office for more information.

# 7.0 AC WRITE SPECIFICATION COMPATIBILITY

In general, write specifications for matching speed bins of bulk erase and Boot Block flash memories are compatible. However, Boot Block devices are functionally different with respect to command writes in two key areas:  $V_{PP}$  command write lockout and WE# address latching.

Unlike their bulk erase counterparts, Boot Block flash memories allow command writes regardless of  $V_{PP}$  voltage applied to them, as long as  $V_{CC}$  is above  $V_{LKO}$  and RP# is above  $V_{IL}$ . This was done to allow full access to array data, Status Register and device identifiers. Program and Erase command sequences written to Boot block devices with  $V_{PP} = V_{PPL}$  will not result in data alteration. In such cases, internal automation will immediately terminate with error indication in the Status Register.

Bulk erase flash memories internally latched addresses on the leading (or falling) edge of WE# and data on WE#'s trailing (or rising) edge. Boot Block devices, on the other hand, latch both addresses and data on WE#'s trailing edge, resulting in a much simpler hardware interface.

Specific AC write specification differences between the 28F001BX and 28F010 are shown in Appendix K.

#### 8.0 SUMMARY

This application note has discussed key considerations when converting designs using bulk erase flash memories to Boot Block devices. Specific component information can be found in device datasheets, listed in Appendix L. Contact your local Intel or distribution sales office for more information or to obtain assistance in evaluating bulk erase and Boot Block flash memory alternatives.

# APPENDIX A DIP PINOUT COMPARISON (28F010 AND 28F001BX)

### APPENDIX B PLCC PINOUT COMPARISON (28F010 AND 28F001BX)

### APPENDIX C TSOP PINOUT COMPARISON (28F010 AND 28F001BX)

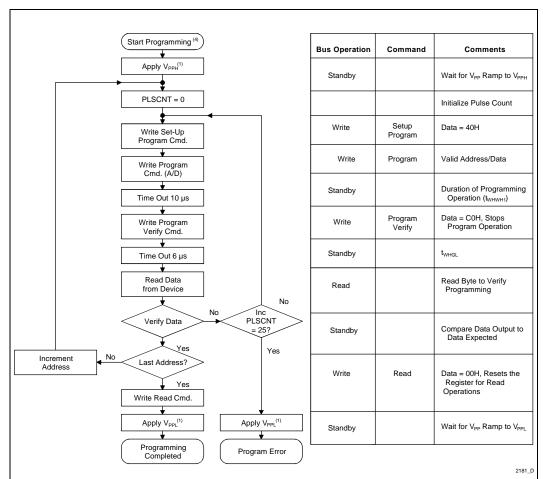

# APPENDIX D BULK ERASE FLASH MEMORY PROGRAM ALGORITHM

NOTES:

- 1. See DC Characteristics for the value of  $V_{\mbox{\footnotesize{PPH}}}$  and  $V_{\mbox{\footnotesize{PPL}}}$ .

- 2. Program Verify is only performed after byte programming. A final read/compare may be performed (operational) after the register is written with the Read command.

- 3. Refer to Principles of Operation.

- 4. CAUTION: The algorithm MUST BE FOLLOWED to ensure proper and reliable operation of the device.

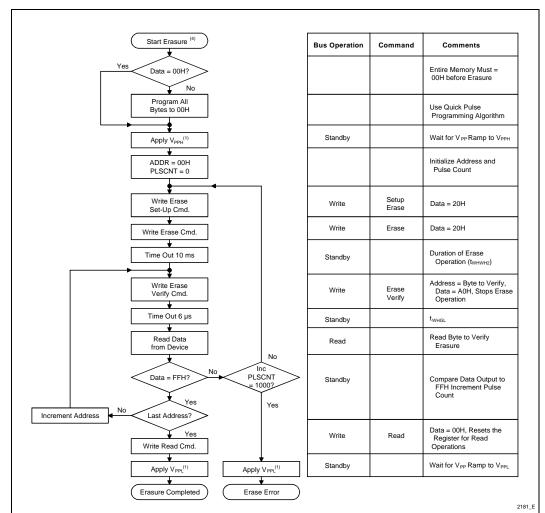

#### APPENDIX E BULK ERASE FLASH MEMORY ERASE ALGORITHM

NOTES:

- 1. See DC Characteristics for the value of  $V_{\mbox{\footnotesize{PPH}}}$  and  $V_{\mbox{\footnotesize{PPL}}}$ .

- 2. Program Verify is only performed after chip erasure. A final read/compare may be performed (operational) after the register is written with the Read command.

- 3. Refer to Principles of Operation.

- 4. CAUTION: The algorithm MUST BE FOLLOWED to ensure proper and reliable operation of the device.

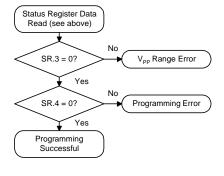

# APPENDIX F BOOT BLOCK FLASH MEMORY AUTOMATED PROGRAM ALGORITHM

| Bus Operation | Command          | Comments                                                                                        |  |  |

|---------------|------------------|-------------------------------------------------------------------------------------------------|--|--|

| Write         | Program<br>Setup | Data = 40H (10H) Address = Location to Be Programmed                                            |  |  |

| Write         | Program          | Data to Be Programmed<br>Address = Location to Be<br>Programmed                                 |  |  |

| Read          |                  | Status Register Data Toggle OE# or CE# to Update Status Register Check SR.7 1 = Ready, 0 = Busy |  |  |

Repeat for subsequent locations.

Full status check can be done after each location or after a sequence of locations.

Write FFH after the last program operation to reset the device to ready/array mode.

#### **FULL STATUS CHECK PROCEDURE**

| Bus Operation | Command | Comments                         |

|---------------|---------|----------------------------------|

| Standby       |         | Check SR.3<br>1 = VPP Low Detect |

| Standby       |         | Check SR.4<br>1 = Program Error  |

SR.3 MUST be cleared, if set during a program attempt, before further attempts are allowed by the Write State Machine.

SR.4 is only cleared by the Clear Status Register command, in cases where multiple locations are programmed before full status is checked.

If error is detected, clear the Status Register before attempting retry or other error recovery.

2181\_

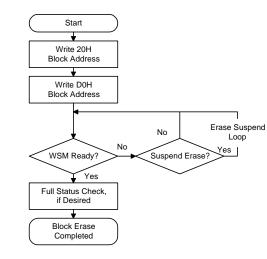

# APPENDIX G BOOT BLOCK FLASH MEMORY AUTOMATED ERASE ALGORITHM

| Bus Operation | Command        | Comments                                                                                        |

|---------------|----------------|-------------------------------------------------------------------------------------------------|

| Write         | Erase<br>Setup | Data = 20H<br>Address = Within Block to<br>Be Erased                                            |

| Write         | Erase          | Data = D0H<br>Address = Within Block to<br>Be Erased                                            |

| Read          |                | Status Register Data Toggle OE# or CE# to Update Status Register Check SR.7 1 = Ready, 0 = Busy |

Repeat for subsequent blocks.

Full status check can be done after each block or after a sequence of blocks

Write FFH after the last block erase operation to reset the device to ready/array mode.

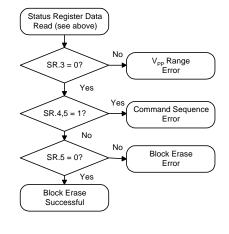

#### **FULL STATUS CHECK PROCEDURE**

| Bus Operation | Command | Comments                                               |

|---------------|---------|--------------------------------------------------------|

| Standby       |         | Check SR.3<br>1 = VPP Low Detect                       |

| Standby       |         | Check SR.4, SR.5<br>Both 1 = Command<br>Sequence Error |

| Standby       |         | Check SR.5<br>1 = Block Erase Error                    |

SR.3 MUST be cleared, if set during a block erase attempt, before further attempts are allowed by the Write State Machine.

SR.5 is only cleared by the Clear Status Register command, in cases where multiple bytes are erased before full status is checked.

If error is detected, clear the Status Register before attempting retry or other error recovery.

2181\_G

#### APPENDIX H **BOOT BLOCK FLASH MEMORY** STATUS REGISTER

| WSMS | ESS | ES | PS | VPPS | R | R | R |

|------|-----|----|----|------|---|---|---|

| 7    | 6   | 5  | 4  | 3    | 2 | 1 | 0 |

again.

#### NOTES:

SR.7 = WRITE STATE MACHINE STATUS

1 = Ready

0 = Busy

The Write State Machine status bit must first be checked to determine program or erase completion before the program or erase status bits are checked for success.

SR.6 = ERASE-SUSPEND STATUS

1 = Erase Suspended

0 = Erase in Progress/Completed

SR.5 = ERASE STATUS

1 = Error in Block Erase

0 = Successful Block Erase

SR.4 = PROGRAM STATUS

1 = Error in Location Program

0 = Successful Location Program

$\begin{array}{l} \text{SR.3} = \text{V}_{\text{PP}} \, \text{STATUS} \\ \text{1} = \text{V}_{\text{PP}} \, \text{Low Detect, Operation Abort} \\ \text{0} = \text{V}_{\text{PP}} \, \text{OK} \\ \end{array}$

If program AND erase status bits are set to "1" during an erase attempt, an improper command sequence was entered. Attempt the operation

The VPPS bit, unlike an A/D converter, does not provide continuous indication of  $V_{PP}$  level. The WSM interrogates  $V_{PP}$ 's level only after the Program or Erase command sequences have been entered, and informs the system if V<sub>PP</sub> has not been switched on. VPPS is not guaranteed to report accurate feedback between V<sub>PPL</sub> and  $V_{PPH}$ .

SR.2-0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use; mask them out when polling the status register.

## APPENDIX I DC SPECIFICATION COMPARISON (28F010 AND 28F001BX)

DC specification differences (commercial temperature) between the 28F010 and 28F001BX flash memories, or specification that exist for one device and not another due to functional differences, are shown below.

#### 28F010

| Symbol           | Parameter                                  | Min | Тур | Max | Unit | Test Condition                                                   |

|------------------|--------------------------------------------|-----|-----|-----|------|------------------------------------------------------------------|

| Iccs             | V <sub>CC</sub> Standby Current (TTL/NMOS) |     | 0.3 | 1.0 | mA   | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE# = V <sub>IH</sub>   |

| I <sub>CC2</sub> | V <sub>CC</sub> Program Current            |     | 1.0 | 10  | mA   | Programming in Progress                                          |

| I <sub>CC3</sub> | V <sub>CC</sub> Erase Current              |     | 5.0 | 15  | mA   | Erasure in Progress                                              |

| I <sub>CC4</sub> | V <sub>CC</sub> Program Verify Current     |     | 5.0 | 15  | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Program Verify in Progress |

| I <sub>CC5</sub> | V <sub>CC</sub> Erase Verify Current       |     | 5.0 | 15  | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress   |

| I <sub>PP4</sub> | V <sub>PP</sub> Program Verify Current     |     | 5.0 | 15  | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Program Verify in Progress |

| I <sub>PP5</sub> | V <sub>PP</sub> Erase Verify Current       |     | 5.0 | 15  | mA   | V <sub>PP</sub> = V <sub>PPH</sub><br>Erase Verify in Progress   |

#### 28F001BX

| Symbol            | Parameter                                  | Min  | Тур  | Max  | Unit | Test Condition                                     |

|-------------------|--------------------------------------------|------|------|------|------|----------------------------------------------------|

| Iccs              | V <sub>CC</sub> Standby Current (TTL/NMOS) |      | 1.2  | 2.0  | mA   | $V_{CC} = V_{CC} Max$<br>$CE\# = RP\# = V_{IH}$    |

| I <sub>CCD</sub>  | V <sub>CC</sub> Deep Power-Down Current    |      | 0.05 | 1.0  | μΑ   | $RP# = GND \pm 0.2V$                               |

| Iccw              | V <sub>CC</sub> Program Current            |      | 5    | 20   | mA   | Programming in Progress                            |

| I <sub>CCE</sub>  | V <sub>CC</sub> Erase Current              |      | 6    | 20   | mA   | Erasure in Progress                                |

| I <sub>CCES</sub> | V <sub>CC</sub> Erase Suspend Current      |      | 5    | 10   | mA   | Erase Suspended, CE# = V <sub>IH</sub>             |

| I <sub>PPD</sub>  | V <sub>PP</sub> Deep Power-Down Current    |      | 0.6  | 1.0  | μΑ   | RP# = GND ± 0.2V                                   |

| I <sub>PPES</sub> | V <sub>PP</sub> Erase Suspend Current      |      | 90   | 400  | μΑ   | V <sub>PP</sub> = V <sub>PPH</sub> , Erase Suspend |

| V <sub>HH</sub>   | Boot Block Unlock Voltage                  | 11.4 |      | 12.6 | V    | Boot Block Prog/Erase                              |

## APPENDIX J AC READ SPECIFICATION COMPARISON (28F010 AND 28F001BX)

AC read specifications (commercial temperature) for the 28F010 and 28F001BX flash memories are shown below:

#### 28F010

|                   | Versions         |                                                                   | 28F0 <sup>-</sup> | 10-120 | 28F010-150 |     |    |

|-------------------|------------------|-------------------------------------------------------------------|-------------------|--------|------------|-----|----|

| Syr               | nbol             | abol Characteristic Min Max Min Max                               |                   | Max    | Unit       |     |    |

| t <sub>AVAV</sub> | t <sub>RC</sub>  | Read Cycle Time                                                   | 120               |        | 150        |     | ns |

| t <sub>ELQV</sub> | t <sub>CE</sub>  | Chip Enable Access Time                                           |                   | 120    |            | 150 | ns |

| t <sub>AVQV</sub> | t <sub>ACC</sub> | Address Access Time                                               |                   | 120    |            | 150 | ns |

| t <sub>GLQV</sub> | t <sub>OE</sub>  | Output Enable Access Time                                         |                   | 50     |            | 55  | ns |

| t <sub>ELQX</sub> | t <sub>LZ</sub>  | Chip Enable to Output in Low Z                                    | 0                 |        | 0          |     | ns |

| t <sub>EHQZ</sub> | t <sub>HZ</sub>  | Chip Disable to Output in High Z                                  |                   | 55     |            | 55  | ns |

| t <sub>GLQX</sub> | t <sub>OLZ</sub> | Output Enable to Output in Low Z                                  | 0                 |        | 0          |     | ns |

| t <sub>GHQZ</sub> | t <sub>DF</sub>  | Output Disable to Output in High Z                                |                   | 30     |            | 30  | ns |

|                   | tон              | Output Hold from Addresses, CE# or OE# Change, Whichever Is First | 0                 |        | 0          |     | ns |

| t <sub>WHGL</sub> |                  | Write Recovery Time before Read                                   | 6                 |        | 6          |     | μs |

#### 28F001BX

| Versions V <sub>C</sub> |                  | V <sub>CC</sub> ± 10%                           | 28F001BX-120 |     | 28F001BX-150 |     |      |    |

|-------------------------|------------------|-------------------------------------------------|--------------|-----|--------------|-----|------|----|

| Symbol Charac           |                  | cteristic                                       | Min          | Max | Min          | Max | Unit |    |

| t <sub>AVAV</sub>       | t <sub>RC</sub>  | Read Cycle Time                                 |              | 120 |              | 150 |      | ns |

| t <sub>AVQV</sub>       | t <sub>ACC</sub> | Address to Output Delay                         |              |     | 120          |     | 150  | ns |

| t <sub>ELQV</sub>       | t <sub>CE</sub>  | CE# to Output Delay                             |              |     | 120          |     | 150  | ns |

| t <sub>PHQV</sub>       | t <sub>PWH</sub> | RP# High to Output Delay                        |              |     | 600          |     | 600  | ns |

| t <sub>GLQV</sub>       | toE              | OE# to Output Delay                             |              |     | 50           |     | 55   | ns |

| t <sub>ELQX</sub>       | t <sub>LZ</sub>  | CE# to Output Low Z                             |              | 0   |              | 0   |      | ns |

| t <sub>EHQZ</sub>       | t <sub>HZ</sub>  | CE# High Output High Z                          |              |     | 55           |     | 55   | ns |

| t <sub>GLQX</sub>       | t <sub>OLZ</sub> | OE# to Output                                   | Low Z        | 0   |              | 0   |      | ns |

| tghqz                   | t <sub>DF</sub>  | OE# High to Output High Z                       |              |     | 30           |     | 30   | ns |

|                         | tон              | Output Hold from CE# or OE# C<br>Whichever Is F |              | 0   |              | 0   |      | ns |

## APPENDIX K AC WRITE SPECIFICATION COMPARISON (28F010 AND 28F001BX)

AC write specification (WE#-controlled write, commercial temperature) differences between the 28F010 and 28F001BX flash memories, or specifications that exist for one device and not another due to functional differences, are shown below:

#### 28F010

| Versions          |                  |                                               | V <sub>CC</sub> ± 10% | 28F01 | 28F010-120 |     | 28F010-150 |    |

|-------------------|------------------|-----------------------------------------------|-----------------------|-------|------------|-----|------------|----|

| Sym               | bol              | Characteristic                                |                       | Min   | Max        | Min | Max        |    |

| t <sub>VPEL</sub> | t <sub>VPS</sub> | V <sub>PP</sub> Setup Time to Chip Enable Low |                       | 1.0   |            | 1.0 |            | μs |

| telwl             | tcs              | Chip Enable Setup Tir                         | 20                    |       | 20         |     | ns         |    |

| t <sub>AVWL</sub> | t <sub>AS</sub>  | Address Setup Time                            | 0                     |       | 0          |     | ns         |    |

| t <sub>WLAX</sub> | t <sub>AH</sub>  | Address Hold Time                             | 50                    |       | 50         |     | ns         |    |

| twLwH             | twp              | Write Pulse Width                             |                       | 60    |            | 60  |            | ns |

| t <sub>WHEH</sub> | t <sub>CH</sub>  | Chip Enable Hold Time                         |                       | 0     |            | 0   |            | ns |

| t <sub>WHWL</sub> | t <sub>WPH</sub> | Write Pulse Width High                        |                       | 20    |            | 20  |            | ns |

#### 28F001BX

| Versions V <sub>CC</sub> ± 10% |                  |                                         | 28F001                             | BX-120 | 28F001BX-150 |     | Unit |    |

|--------------------------------|------------------|-----------------------------------------|------------------------------------|--------|--------------|-----|------|----|

| Symbol                         |                  | Characteristic                          |                                    | Min    | Max          | Min | Max  |    |

| t <sub>PHWL</sub>              | t <sub>PS</sub>  | RP# High Recovery to                    | RP# High Recovery to WE# Going Low |        |              | 480 |      | ns |

| t <sub>ELWL</sub>              | t <sub>CS</sub>  | CE# Setup to WE# Go                     | oing Low                           | 10     |              | 10  |      | ns |

| twLwH                          | twp              | WE# Pulse Width                         | 50                                 |        | 50           |     | ns   |    |

| t <sub>PHHWH</sub>             | t <sub>PHS</sub> | RP# V <sub>HH</sub> Setup to WE         | 100                                |        | 100          |     | ns   |    |

| t <sub>VPWH</sub>              | t <sub>VPS</sub> | V <sub>PP</sub> Setup to WE# Go         | 100                                |        | 100          |     | ns   |    |

| t <sub>AVWH</sub>              | t <sub>AS</sub>  | Address Setup to WE                     | 50                                 |        | 50           |     | ns   |    |

| t <sub>WHAX</sub>              | t <sub>AH</sub>  | Address Hold from WI                    | 10                                 |        | 10           |     | ns   |    |

| t <sub>WHEH</sub>              | t <sub>CH</sub>  | CE# Hold from WE# High                  |                                    | 10     |              | 10  |      | ns |

| twhwL                          | twph             | WE# Pulse Width High                    |                                    | 50     |              | 50  |      | ns |

| t <sub>WHGL</sub>              |                  | Write Recovery before Read              |                                    | 0      |              | 0   |      | μs |

| t <sub>QVVL</sub>              | t∨PH             | V <sub>PP</sub> Hold from Valid SRD     |                                    | 0      |              | 0   |      | ns |

| t <sub>QVPH</sub>              | t <sub>PHH</sub> | RP# V <sub>HH</sub> Hold from Valid SRD |                                    | 0      |              | 0   |      | ns |

| t <sub>PHBR</sub>              |                  | Boot Block Relock Delay                 |                                    |        | 100          |     | 100  | ns |

# APPENDIX L INTEL BULK ERASE AND BOOT BLOCK FLASH MEMORY RELATED DATASHEETS

#### **Bulk Erase Flash Memories**

| Order<br>Number | Document                                            |  |  |  |

|-----------------|-----------------------------------------------------|--|--|--|

| 290245          | 28F020 2048K (256K x 8) CMOS Flash Memory Datasheet |  |  |  |

| 290208          | 28F010 1024K (128K x 8) CMOS Flash Memory Datasheet |  |  |  |

| 290204          | 28F512 512K (64K x 8) CMOS Flash Memory Datasheet   |  |  |  |

| 290246          | 28F256A 256K (32K x 8) CMOS Flash Memory Datasheet  |  |  |  |

#### **Boot Block Flash Memories**

| Order<br>Number | Document                                                                            |  |  |  |

|-----------------|-------------------------------------------------------------------------------------|--|--|--|

| 290539          | 8-Mbit (512K x 16, 1024K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet |  |  |  |

| 290530          | 4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet  |  |  |  |

| 290531          | 2-Mbit (128K x 16, 256K x 8) SmartVoltage Boot Block Flash Memory Family Datasheet  |  |  |  |

| 290450          | 4-Mbit (256K x 16, 512K x 8) Low-Power Boot Block Flash Memory Family Datasheet     |  |  |  |

| 290451          | 4-Mbit (256K x 16, 512K x 8) Boot Block Flash Memory Family Datasheet               |  |  |  |

| 290449          | 2-Mbit (128K x 16, 256K x 8) Low-Power Boot Block Flash Memory Family Datasheet     |  |  |  |

| 290448          | 2-Mbit (128K x 16, 256K x 8) Boot Block Flash Memory Family Datasheet               |  |  |  |

| 290406          | 1-Mbit (128K x 8) Boot Block Flash Memory Datasheet                                 |  |  |  |

For more information on bulk erase and boot block flash memories, please consult the Intel World Wide Web Home Page: http://www.intel.com.