# **SERIES 2+ FLASH MEMORY CARDS** 4-, 8-, 20- AND 40-MEGABYTE

iMC004FLSP, iMC008FLSP, iMC020FLSP, iMC040FLSP

- Single Power Supply

- Automatically Reconfigures for 3.3V and 5V Systems

- 150 ns Maximum Access Time with 5V **Power Supply**

- 250 ns Maximum Access Time with 3.3V Power Supply

- High-Performance Random Writes

- 0.85 MB/S Sustained Throughput

- 1 KB Burst Write at 10 MB/S

- 12 µA Typical Deep Power-Down

- Revolutionary Architecture

- Pipelined Command Execution

- Write during Erase

- Series 2 Command Super-Set

- State-of-the-Art 0.6 µm ETOX™ IV Flash **Technology**

- 1 Million Erase Cycles per Block

- Up to 640 Independent Lockable Blocks

Order Number: 290491-006

- PCMCIA 2.1/JEIDA 4.1-Compatible

- PCMCIA Type 1 Form Factor

- Series 2+ User's Manual

Intel's Series 2+ Flash Memory Card sets the new record for high-performance disk emulation and eXecute-In-Place (XIP) applications in mobile PCs and dedicated equipment. Manufactured with Intel's 28F016SA 16-Mbit (DD28F032SA 32-Mbit) FlashFile™ memory, this card takes advantage of a revolutionary architecture that provides innovative capabilities, low-power operation and very high read/write performance.

The Series 2+ card provides today's highest density, highest performance nonvolatile read/write solution for solid-state storage applications. These applications are enhanced further with this product's symmetricallyblocked architecture, extended MTBF, low-power 3.3V operation, built-in VPP generator, and multiple block locking methods. The Series 2+ card's dual read and write voltages allow interchange between 3.3V and 5.0V systems.

PAGE

# **CONTENTS**

| PAGE                                                                             |

|----------------------------------------------------------------------------------|

| 1.0 SCOPE OF DOCUMENT3                                                           |

| 2.0 PRODUCT OVERVIEW3                                                            |

| 3.0 SERIES 2+ ARCHITECTURE OVERVIEW4         3.1 Card Pinout and Pin Description |

| 4.0 DEVICE COMMAND SET14                                                         |

| 5.0 DEVICE STATUS REGISTER17                                                     |

| 6.0 PCMCIA CARD INFORMATION STRUCTURE18                                          |

| 7.0 SYSTEM DESIGN CONSIDERATIONS22                                               |

| 7.1 Power Supply Decoupling22                                                    |

| 7.2 Power-Up/Down Protection22                                                   |

| 7.3 Hot Insertion/Removal22                                                      |

| 8.0 ELECTRICAL SPECIFICATIONS23                                                  |

| 8.1 Absolute Maximum Ratings23                                                   |

| 9.0 SERIES 2+ DC CHARACTERISTICS24                                               |

| 9.1 General24                                                                    |

| 9.2 CMOS Interfacing: V <sub>CC</sub> = 3.3V25                                   |

| 9.3 CMOS Interfacing: V <sub>CC</sub> = 5.0V25                                   |

| 9.4 TTL Interfacing: V <sub>CC</sub> = 3.3V27                                    |

| 9.5 TTL Interfacing: V <sub>CC</sub> = 5.0V28                                    |

| 100 4                              | C CHARACTERISTICS29                                                 |

|------------------------------------|---------------------------------------------------------------------|

|                                    |                                                                     |

|                                    | Read Operations: Common and Attribute                               |

|                                    | mory29                                                              |

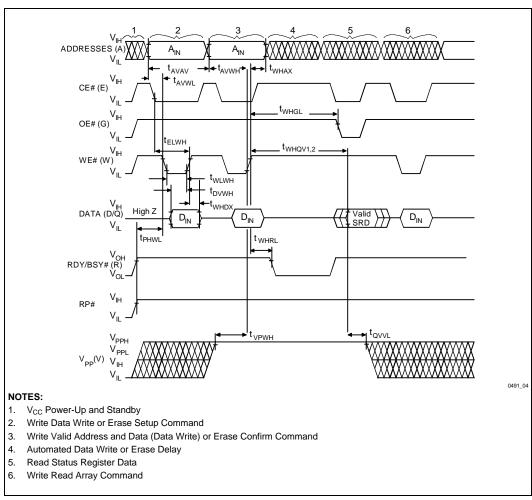

|                                    | Write Operations: Common and Attribute                              |

| Me                                 | mory31                                                              |

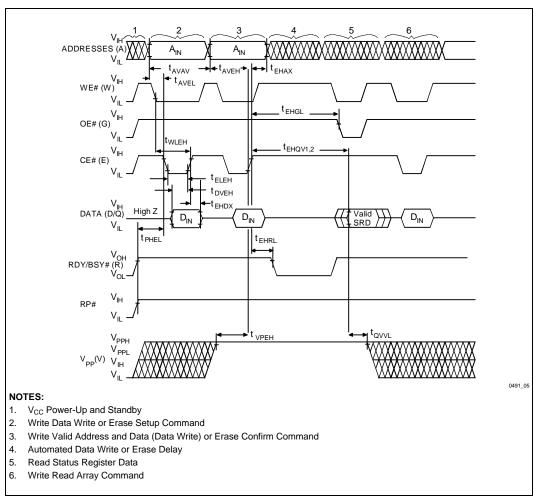

| 10.3                               | CE#-Controlled Write Operations:                                    |

| Co                                 | mmon and Attribute Memory33                                         |

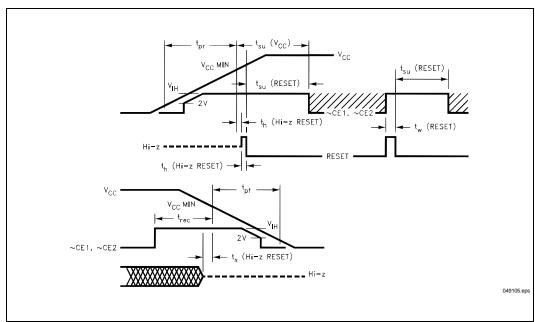

| 10.4                               | Power-Up/Power-Down35                                               |

| 10.5                               | Series 2+ Card Information Structure                                |

| Tu                                 | ole Changes36                                                       |

|                                    |                                                                     |

|                                    |                                                                     |

| 11.0 C                             | APACITANCE36                                                        |

|                                    |                                                                     |

| 12.0 E                             | RASE AND DATA WRITE                                                 |

| 12.0 E                             |                                                                     |

| 12.0 E<br>PERI                     | RASE AND DATA WRITE                                                 |

| 12.0 E<br>PERI<br>13.0 P           | RASE AND DATA WRITE FORMANCE37 ACKAGING38                           |

| 12.0 E<br>PERI<br>13.0 P           | RASE AND DATA WRITE FORMANCE37                                      |

| 12.0 E<br>PERI<br>13.0 P           | RASE AND DATA WRITE FORMANCE37 ACKAGING38                           |

| 12.0 E<br>PERI<br>13.0 P<br>14.0 A | RASE AND DATA WRITE FORMANCE37 PACKAGING38 ADDITIONAL INFORMATION40 |

## 1.0 SCOPE OF DOCUMENT

The documentation for Intel's Series 2+ Flash Memory Card includes this datasheet and the Series 2+ Flash Memory Card User's Manual (297373). The datasheet provides all AC and DC characteristics (including timing waveforms) and a convenient reference for the device command set and the card's integrated registers (including the 28F016SA's status registers). The Series 2+ Memory Card User's Manual provides a complete description of the methods for using the card. It also contains the full list of software algorithms and flowcharts and a section for upgrading Intel's Series 2 Flash Memory Cards designs.

## 2.0 PRODUCT OVERVIEW

The 4-, 8-, and 20- Megabyte Series 2+ Flash Memory Cards each contain a flash memory array that consists of two, four, and ten 28F016SA TSOP memory devices, respectively. Each 28F016SA contains 32 distinct, individually-erasable, 64-Kbyte blocks. Therefore, the 4-, 8-, and 20-megabyte cards contain 64, 128 and 320 independently lockable blocks, respectively.

The 40-Megabyte Series 2+ Flash Memory Cards contain a flash memory array that consists of ten DD28F032SA TSOP memory devices. Each DD28F032SA contains two 28F016SA die in a single package, resulting in 64 distinct, individuallyerasable, 64-Kbyte blocks. The 40-megabyte cards have 640 independently lockable blocks.

The Series 2+ Card offers additional product features to those of the Series 2 Card family (refer to the iMC0XXFLSA datasheets). Some of the more notable card-level enhancements include: interchangeable operation at 3.3V or 5.0V, block locking and internal  $V_{PP}$  generation.

The Series 2+ card incorporates  $V_{CC}$  detect circuitry, referred to as SmartPower, to sense the voltage level present at the card interface. The card's control logic automatically configures its circuitry and the 28F016SA/DD28F032SA memory array accordingly. The Card Information Structure (CIS) reports that the card is 3.3V or 5.0V compatible. The card also detects the presence of 12.0V on the  $V_{PP}$  pin and passes this supply to each memory device. When the 12.0V power supply is unavailable, the card can generate the

required  $V_{PP}$  via its internal  $V_{PP}$  generation circuitry, whether  $V_{CC}$  is 3.3V or 5.0V.

At the device level, internal algorithm automation allows Write and Erase operations to be executed using a two-write command sequence in the same way as the 28F008SA FlashFile memory in the Series 2 Card. A super-set of commands and additional performance enhancements have been added to the basic 28F008SA command set:

- Page Buffer Write to Flash results in writes up to four times faster than Series 2 Cards.

- Command Queueing permits the devices to receive new commands during the execution of the current command set.

- Automatic data writes during erase allows the 28F016SA to perform Write operations to one block of memory while performing an Erase on another block.

- Software locking of memory blocks provides a means to selectively protect code or data within the card.

- Erase all unlocked blocks provides a quick and simple method to sequentially erase all the blocks within a 28F016SA memory device.

The Series 2+ Card has two ways to put the flash devices into a sleep mode for reduced power consumption:

- Issue a command to individual devices, referred to as the software-controlled sleep mode. The device will retain status register data contents and finish any operation in progress using this approach.

- Write to the card's PCMCIA-compatible Configuration and Status Register to activate a Reset Power-Down to all devices simultaneously.

The card achieves its PCMCIA-compatible wordwide access by pairing the 28F016SA/DD28F032SA devices resulting in an accessible memory block size of 64 Kwords. The card's decoding logic (contained within the ASICs) allows the system to write or read one word at a time, or one byte at a time by referencing the high or low byte. Erasure can be performed on the entire block pair (high and low byte simultaneously) or on the high and low portions separately. Although the 28F016SA/DD28F032SA support byte or word-wide

#### SERIES 2+ FLASH MEMORY CARDS

data access, the byte interface was utilized within the card to allow the delivery of higher performance benefits, such as doubling the effective page buffer size and write performance.

The Series 2+ Card's ASICs also contain the Component Management Registers that provide five control functions: Ready-Busy Mode Selection, Software Write Protection, Card Status, Voltage Control, and Soft Reset.

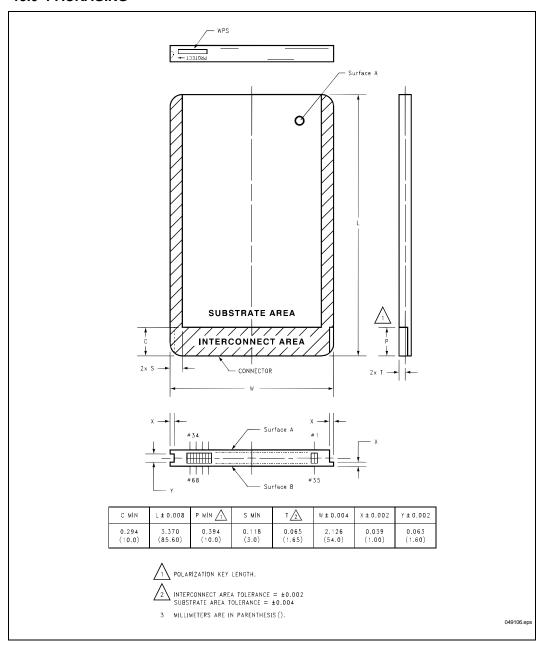

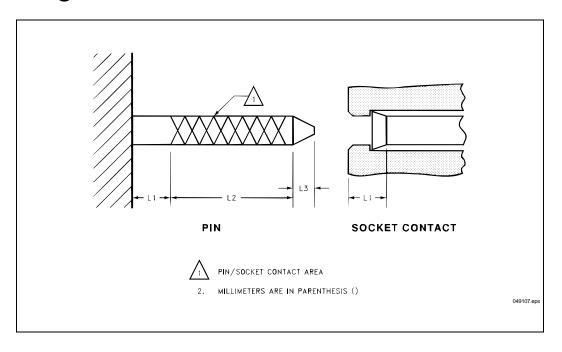

The memory card interface supports the Personal Computer Memory Card Industry Association (PCMCIA 2.10) and Japanese Electronics Industry Development Association (JEIDA 4.1) 68-pin card format. The Series 2+ Flash Card meets all PCMCIA/JEIDA Type 1 mechanical specifications.

# 3.0 SERIES 2+ ARCHITECTURE OVERVIEW

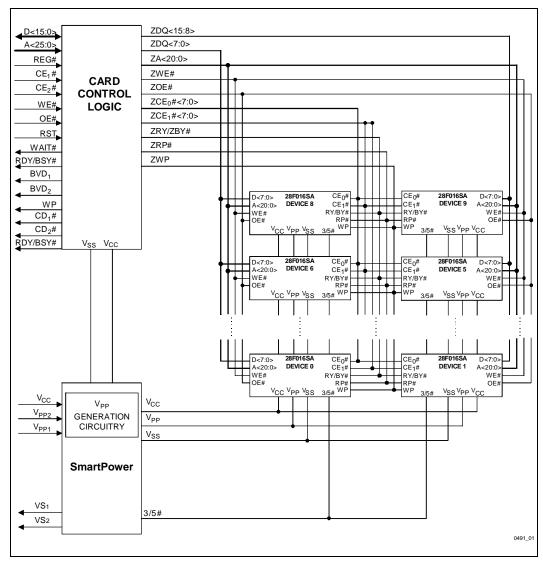

The Series 2+ Card consists of three major functional elements—the flash memory array, card control and SmartPower circuitry. The card control logic handles the interface between the flash memory array and the host system's PCMCIA signals. SmartPower circuitry provides the card's integrated V<sub>PP</sub> generator and a means for detecting the socket's voltage levels.

## 3.1 Card Pinout and Pin Description

The 68-pin PCMCIA format provides the system interface for the Series 2+ Flash Memory Card (see Tables 1 and 2). The detailed specifications for this interface is described in the PCMCIA 2.10 Standard Specification. The Series 2+ Flash Card product family conforms to the requirements of previous PCMCIA Versions Release 1.0, Release 2.0 and Release 2.01 of the PC Card Standard. Release 2.10 redefined pins 43 and 57 as VS<sub>1</sub> and VS<sub>2</sub> (previously REFRESH and RFU, respectively).

Figure 1. Series 2+ Flash Memory Card Block Diagram Showing Major Functional Elements

Table 1. Series 2+ Flash Memory Card Signals

| Pin | Signal            | I/O | Function       | Active |

|-----|-------------------|-----|----------------|--------|

| 1   | GND               |     | Ground         |        |

| 2   | 2 DQ <sub>3</sub> |     | Data Bit 3     |        |

| 3   | DQ <sub>4</sub>   | I/O | Data Bit 4     |        |

| 4   | DQ <sub>5</sub>   | I/O | Data Bit 5     |        |

| 5   | DQ <sub>6</sub>   | I/O | Data Bit 6     |        |

| 6   | DQ <sub>7</sub>   | I/O | Data Bit 7     |        |

| 7   | CE <sub>1</sub> # | I   | Card Enable 1  | LOW    |

| 8   | A <sub>10</sub>   | I   | Address Bit 10 |        |

| 9   | OE#               | I   | Output Enable  | LOW    |

| 10  | A <sub>11</sub>   | I   | Address Bit 11 |        |

| 11  | A <sub>9</sub>    | I   | Address Bit 9  |        |

| 12  | A <sub>8</sub>    | I   | Address Bit 8  |        |

| 13  | A <sub>13</sub>   | I   | Address Bit 13 |        |

| 14  | A <sub>14</sub>   | I   | Address Bit 14 |        |

| 15  | WE#               | I   | Write Enable   | LOW    |

| 16  | RDY/BSY#          | 0   | Ready/Busy     | LOW    |

| 17  | V <sub>CC</sub>   |     | Supply Voltage |        |

| 18  | V <sub>PP1</sub>  |     | Supply Voltage |        |

| 19  | A <sub>16</sub>   | Ι   | Address Bit 16 |        |

| 20  | A <sub>15</sub>   | -   | Address Bit 15 |        |

| 21  | A <sub>12</sub>   | -   | Address Bit 12 |        |

| 22  | A <sub>7</sub>    | I   | Address Bit 7  |        |

| 23  | A <sub>6</sub>    | I   | Address Bit 6  |        |

| 24  | A <sub>5</sub>    | I   | Address Bit 5  |        |

| 25  | A <sub>4</sub>    | I   | Address Bit 4  |        |

| 26  | A <sub>3</sub>    | I   | Address Bit 3  |        |

| Memory Card Signals |                   |     |                 |        |  |  |  |  |  |

|---------------------|-------------------|-----|-----------------|--------|--|--|--|--|--|

| Pin                 | Signal            | I/O | Function        | Active |  |  |  |  |  |

| 27                  | A <sub>2</sub>    | I   | Address Bit 2   |        |  |  |  |  |  |

| 28                  | A <sub>1</sub>    | I   | Address Bit 1   |        |  |  |  |  |  |

| 29                  | A <sub>0</sub>    | I   | Address Bit 0   |        |  |  |  |  |  |

| 30                  | $DQ_0$            | I/O | Data Bit 0      |        |  |  |  |  |  |

| 31                  | DQ <sub>1</sub>   | I/O | Data Bit 1      |        |  |  |  |  |  |

| 32                  | DQ <sub>2</sub>   | I/O | Data Bit 2      |        |  |  |  |  |  |

| 33                  | WP                | 0   | Write Protect   | HIGH   |  |  |  |  |  |

| 34                  | GND               |     | Ground          |        |  |  |  |  |  |

| 35                  | GND               |     | Ground          |        |  |  |  |  |  |

| 36                  | CD <sub>1</sub> # | 0   | Card Detect 1   | LOW    |  |  |  |  |  |

| 37                  | DQ <sub>11</sub>  | I/O | Data Bit 11     |        |  |  |  |  |  |

| 38                  | DQ <sub>12</sub>  | I/O | Data Bit 12     |        |  |  |  |  |  |

| 39                  | DQ <sub>13</sub>  | I/O | Data Bit 13     |        |  |  |  |  |  |

| 40                  | DQ <sub>14</sub>  | I/O | Data Bit 14     |        |  |  |  |  |  |

| 41                  | DQ <sub>15</sub>  | I/O | Data Bit 15     |        |  |  |  |  |  |

| 42                  | CE <sub>2</sub> # | _   | Card Enable 2   | LOW    |  |  |  |  |  |

| 43                  | VS <sub>1</sub>   | 0   | Voltage Sense 1 | LOW    |  |  |  |  |  |

| 44                  | RFU               |     | Reserved        |        |  |  |  |  |  |

| 45                  | RFU               |     | Reserved        |        |  |  |  |  |  |

| 46                  | A <sub>17</sub>   | _   | Address Bit 17  |        |  |  |  |  |  |

| 47                  | A <sub>18</sub>   | _   | Address Bit 18  |        |  |  |  |  |  |

| 48                  | A <sub>19</sub>   | I   | Address Bit 19  |        |  |  |  |  |  |

| 49                  | A <sub>20</sub>   | I   | Address Bit 20  |        |  |  |  |  |  |

| 50                  | A <sub>21</sub>   | I   | Address Bit 21  |        |  |  |  |  |  |

| 51                  | V <sub>CC</sub>   |     | Supply Voltage  |        |  |  |  |  |  |

| 52                  | V <sub>PP2</sub>  |     | Supply Voltage  |        |  |  |  |  |  |

|                     |                   |     |                 |        |  |  |  |  |  |

Table 1. Series 2+ Flash Memory Card Signals (Continued)

| Pin | Signal          | I/O | Function            | Active |

|-----|-----------------|-----|---------------------|--------|

| 53  | A <sub>22</sub> | I   | Address Bit 22      |        |

| 54  | A <sub>23</sub> | I   | Address Bit 23      |        |

| 55  | A <sub>24</sub> | I   | Address Bit 24      |        |

| 56  | A <sub>25</sub> | I   | Address Bit 25      |        |

| 57  | VS <sub>2</sub> | 0   | Voltage Sense 2     | N.C.   |

| 58  | RST             | I   | Reset               | HIGH   |

| 59  | WAIT#           | 0   | Extend Bus<br>Cycle | LOW    |

| 60  | RFU             |     | Reserved            |        |

| Pin | Signal            | I/O | Function                    | Active |

|-----|-------------------|-----|-----------------------------|--------|

| 61  | REG#              | I   | Attribute Memory<br>Select  | LOW    |

| 62  | BVD <sub>2</sub>  | 0   | Battery Voltage<br>Detect 2 |        |

| 63  | BVD <sub>1</sub>  | 0   | Battery Voltage<br>Detect 1 |        |

| 64  | DQ <sub>8</sub>   | I/O | Data Bit 8                  |        |

| 65  | $DQ_9$            | I/O | Data Bit 9                  |        |

| 66  | DQ <sub>10</sub>  | I/O | Data Bit 10                 |        |

| 67  | CD <sub>2</sub> # | 0   | Card Detect 2               | LOW    |

| 68  | GND               |     | Ground                      |        |

Table 2. Series 2+ Flash Memory Card Signal Description

| Symbol                              | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>25</sub>     | INPUT            | <b>ADDRESS INPUTS:</b> Address $A_0$ through $A_{25}$ are address bus lines which enable direct addressing of up to 64 megabytes of memory on the card. Signal $A_0$ is not used in word access mode. $A_{25}$ is the most significant bit.                                                                                                                                                                  |

| DQ <sub>0</sub> –DQ <sub>15</sub>   | INPUT/<br>OUTPUT | <b>DATA INPUT/OUTPUT:</b> $DQ_0$ through $DQ_{15}$ constitute the bi-directional data bus. $DQ_{15}$ is the most significant bit.                                                                                                                                                                                                                                                                            |

| CE <sub>1</sub> #,CE <sub>2</sub> # | INPUT            | <b>CARD ENABLE 1 &amp; 2:</b> $CE_1\#$ enables even bytes, $CE_2\#$ enables odd bytes. Multiplexing $A_0$ , $CE_1\#$ and $CE_2\#$ allows 8-bit hosts to access all data on $D_0$ through $D_7$ .                                                                                                                                                                                                             |

| OE#                                 | INPUT            | OUTPUT ENABLE: Active low signal gating read data from the memory card.                                                                                                                                                                                                                                                                                                                                      |

| WE#                                 | INPUT            | WRITE ENABLE: Active low signal gating write data to the memory card.                                                                                                                                                                                                                                                                                                                                        |

| RDY/BSY#                            | OUTPUT           | READY/BUSY OUTPUT: Indicates status of internally timed erase or write activities. A high output indicates the memory card is ready to accept accesses. A low output indicates that a device in the memory card is busy with internally timed erase or write activities.                                                                                                                                     |

| CD <sub>1</sub> #,CD <sub>2</sub> # | OUTPUT           | CARD DETECT 1 & 2: These signals provide for correct memory card insertion detection. They are positioned at opposite ends of the card to detect proper alignment. The signals are connected to ground internally on the memory card, and will be forced low whenever a card is placed in the socket. The host socket interface circuitry shall supply 10K or larger pull-up resistors on these signal pins. |

Table 2. Series 2+ Flash Memory Card Signal Description (Continued)

| Symbol                                 | Туре   | Name and Function                                                                                                                                                                                                                                                                                                    |

|----------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WP                                     | OUTPUT | WRITE PROTECT: Write Protect reflects the status of the Write Protect switch on the memory card. WP set to high = write protected, providing internal hardware write lockout to the flash array.                                                                                                                     |

| V <sub>PP1</sub> ,V <sub>PP2</sub>     |        | WRITE/ERASE POWER SUPPLY: (12V nominal) for erasing memory array blocks or writing bytes in the array. These pins must be 12V to perform and Write/Erase operation when not using the card's integrated V <sub>PP</sub> generator. These signals may be disconnected but are required for ExCA™ standard compliance. |

| V <sub>CC</sub>                        |        | CARD POWER SUPPLY: (3.3V or 5V nominal) for all internal circuitry.                                                                                                                                                                                                                                                  |

| GND                                    |        | GROUND for all internal circuitry.                                                                                                                                                                                                                                                                                   |

| REG#                                   | INPUT  | REGISTER SELECT: Provides access to Series 2+ Flash Memory Card registers and Card Information Structure in the Attribute Memory Plane.                                                                                                                                                                              |

| RST                                    | INPUT  | RESET: Active high signal for placing card in Power-On Default State.                                                                                                                                                                                                                                                |

| WAIT#                                  | OUTPUT | WAIT: (Extend Bus Cycle) This signal is driven high for compatibility.                                                                                                                                                                                                                                               |

| BVD <sub>1</sub> ,<br>BVD <sub>2</sub> | OUTPUT | <b>BATTERY VOLTAGE DETECT:</b> These signals are driven high to maintain SRAM card compatibility.                                                                                                                                                                                                                    |

| VS <sub>1</sub> , VS <sub>2</sub>      | OUTPUT | <b>VOLTAGE SENSE:</b> Notify the host socket of the card's $V_{CC}$ requirements. $VS_1$ grounded and $VS_2$ open indicates a 3.3V/5V card has been inserted.                                                                                                                                                        |

| RFU                                    |        | RESERVED FOR FUTURE USE                                                                                                                                                                                                                                                                                              |

| N.C.                                   |        | NO INTERNAL CONNECTION TO CARD; pin may be driven or left floating.                                                                                                                                                                                                                                                  |

#### SERIES 2+ FLASH MEMORY CARDS

# 3.2 Series 2+ Card Control Logic

The Card Control Logic, contained within two ASICS, handles the address decoding and data control for the Series 2+ Card. The Component Management Registers are also contained within the Card Control Logic.

#### 3.2.1 ADDRESS DECODE LOGIC

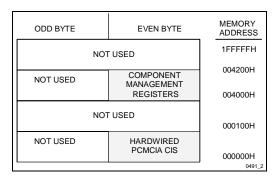

At the highest level, the Address Decode section determines when to select the Common Memory (REG# =  $V_{IH}$ ) or Attribute Memory (REG# =  $V_{IL}$ ) Planes. Within the Attribute Memory Plane ( Figure 2) , the address decode logic determines when to select the Card Information Structure (CIS) or Component Management Registers (CMR). The CIS contains tuple information and is located at even-byte addresses beginning with address 0000H (refer to Section 6.0). The Component Management Registers are mapped at even byte locations beginning at address 4000H (refer to Section 3.3 for a detailed description).

Figure 2. Attribute Memory Plane

#### 3.2.2 DATA CONTROL

As shown in Table 3, data paths and directions are selected by the Data Control logic using REG#,  $A_0$ , WE#, OE#, CE<sub>1</sub>#, and CE<sub>2</sub># as logic inputs. The Data Control logic selects any of the PCMCIA wordwide, byte-wide, and odd-byte modes for either Reads or Writes to Common or Attribute Memory. All accesses to the Attribute Memory Plane must be made through D[7:0] no valid data can be written on the high byte. Reads of D[15:8] will yield FFH.

Table 3. Data Access Mode Truth Table

|                                                                                                                  | COMMON MEMORY PLANE |          |                 |          |                 |                 |           |           |        |        |  |  |

|------------------------------------------------------------------------------------------------------------------|---------------------|----------|-----------------|----------|-----------------|-----------------|-----------|-----------|--------|--------|--|--|

| Mode REG# CE <sub>2</sub> # CE <sub>1</sub> # A <sub>0</sub> OE# WE# V <sub>PP2</sub> V <sub>PP1</sub> D[15:8] I |                     |          |                 |          |                 |                 |           |           |        |        |  |  |

| Standby                                                                                                          | Х                   | $V_{IH}$ | $V_{IH}$        | Χ        | Х               | Х               | $V_{PPL}$ | $V_{PPL}$ | High-Z | High-Z |  |  |

| Byte-Read                                                                                                        | V <sub>IH</sub>     | $V_{IH}$ | $V_{IL}$        | $V_{IL}$ | $V_{IL}$        | V <sub>IH</sub> | $V_{PPL}$ | $V_{PPL}$ | High-Z | Even   |  |  |

|                                                                                                                  | V <sub>IH</sub>     | $V_{IH}$ | $V_{IL}$        | $V_{IH}$ | $V_{IL}$        | $V_{IH}$        | $V_{PPL}$ | $V_{PPL}$ | High-Z | Odd    |  |  |

| Word-Read                                                                                                        | $V_{IH}$            | $V_{IL}$ | $V_{IL}$        | Χ        | $V_{IL}$        | $V_{IH}$        | $V_{PPL}$ | $V_{PPL}$ | Odd    | Even   |  |  |

| Odd Byte-Read                                                                                                    | V <sub>IH</sub>     | $V_{IL}$ | $V_{IH}$        | Χ        | $V_{IL}$        | $V_{IH}$        | $V_{PPL}$ | $V_{PPL}$ | Odd    | High-Z |  |  |

| Byte-Write                                                                                                       | $V_{IH}$            | $V_{IH}$ | $V_{IL}$        | $V_{IL}$ | V <sub>IH</sub> | $V_{IL}$        | XXX       | $V_{PPH}$ | XXX    | Even   |  |  |

|                                                                                                                  | $V_{IH}$            | $V_{IH}$ | $V_{IL}$        | $V_{IH}$ | $V_{IH}$        | $V_{IL}$        | $V_{PPH}$ | XXX       | XXX    | Odd    |  |  |

| Word-Write                                                                                                       | V <sub>IH</sub>     | $V_{IL}$ | $V_{IL}$        | Χ        | V <sub>IH</sub> | $V_{IL}$        | $V_{PPH}$ | $V_{PPH}$ | Odd    | Even   |  |  |

| Odd Byte-Write                                                                                                   | $V_{IH}$            | $V_{IL}$ | V <sub>IH</sub> | Χ        | V <sub>IH</sub> | $V_{IL}$        | $V_{PPH}$ | $V_{PPL}$ | Odd    | XXX    |  |  |

Table 3. Data Access Mode Truth Table (Continued)

|                                                                                                                           | ATTRIBUTE MEMORY PLANE |          |                 |                 |                 |                 |           |           |        |        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-----------------|-----------------|-----------------|-----------------|-----------|-----------|--------|--------|--|--|--|

| Mode REG# CE <sub>2</sub> # CE <sub>1</sub> # A <sub>0</sub> OE# WE# V <sub>PP2</sub> V <sub>PP1</sub> D <sub>[15:8</sub> |                        |          |                 |                 |                 |                 |           |           |        |        |  |  |  |

| Standby                                                                                                                   | Χ                      | $V_{IH}$ | $V_{IH}$        | Х               | Χ               | Χ               | $V_{PPL}$ | $V_{PPL}$ | High-Z | High-Z |  |  |  |

| Byte-Read                                                                                                                 | $V_{IL}$               | $V_{IH}$ | $V_{IL}$        | $V_{IL}$        | $V_{IL}$        | V <sub>IH</sub> | $V_{PPL}$ | $V_{PPL}$ | High-Z | Even   |  |  |  |

|                                                                                                                           | V <sub>IL</sub>        | $V_{IH}$ | $V_{IL}$        | V <sub>IH</sub> | $V_{IL}$        | V <sub>IH</sub> | $V_{PPL}$ | $V_{PPL}$ | High-Z | FFH    |  |  |  |

| Word-Read                                                                                                                 | $V_{IL}$               | $V_{IL}$ | $V_{IL}$        | Х               | $V_{IL}$        | $V_{IH}$        | $V_{PPL}$ | $V_{PPL}$ | FFH    | Even   |  |  |  |

| Odd Byte-Read                                                                                                             | $V_{IL}$               | $V_{IL}$ | $V_{IH}$        | Х               | $V_{IL}$        | $V_{IH}$        | $V_{PPL}$ | $V_{PPL}$ | FFH    | High-Z |  |  |  |

| Byte-Write                                                                                                                | $V_{IL}$               | $V_{IH}$ | $V_{IL}$        | $V_{IL}$        | V <sub>IH</sub> | $V_{IL}$        | $V_{PPL}$ | $V_{PPL}$ | XXX    | Even   |  |  |  |

|                                                                                                                           | $V_{IL}$               | $V_{IH}$ | $V_{IL}$        | $V_{IH}$        | $V_{IH}$        | $V_{IL}$        | $V_{PPL}$ | $V_{PPL}$ | XXX    | XXX    |  |  |  |

| Word-Write                                                                                                                | $V_{IL}$               | $V_{IL}$ | $V_{IL}$        | Х               | V <sub>IH</sub> | $V_{IL}$        | $V_{PPL}$ | $V_{PPL}$ | XXX    | Even   |  |  |  |

| Odd Byte-Write                                                                                                            | $V_{IL}$               | $V_{IL}$ | V <sub>IH</sub> | Х               | V <sub>IH</sub> | $V_{IL}$        | $V_{PPL}$ | $V_{PPL}$ | XXX    | XXX    |  |  |  |

#### NOTES:

When using the  $V_{PP}$  generator,  $V_{PP1}$  and  $V_{PP2}$  are "don't care."

# 3.3 Component Management Registers

The Component Management Registers (CMRs) are classified into two categories: those defined by PCMCIA Rev 2.0, and those included by Intel to enhance the interface between the host system and the card's flash memory array. The CMRs provide five control functions: Ready-Busy Mode selection, Voltage Control, Software Write Protection, Card Status and Soft Reset. For more details about the Component Management Register functionality, consult Intel's Series 2+ Flash Memory Card User's Manual (297373).

## 3.4 SmartPower

The SmartPower circuitry generates and monitors the card's programming voltages. When a host system does not provide a valid  $V_{PP}$  supply, the card's integrated generator can be switched on via the Voltage Control Register. The SmartPower circuitry also detects the host system's  $V_{CC}$  level (3.3V or 5.0V) and configures the card's flash memory devices, accordingly driving the 3/5# pin to the memory array to the appropriate value.

The SmartPower circuitry is enabled by writing a "1" to Bit 0 of the Voltage Control Register.

# Table 4. Configuration Option Register - PCMCIA (Soft Reset Register)

|   | Attribute Memory Plane Address: 4000H<br>Read/Write |         |   |   |           |                                              |              |                |  |  |

|---|-----------------------------------------------------|---------|---|---|-----------|----------------------------------------------|--------------|----------------|--|--|

|   | SRESET                                              | LevIREQ |   |   | Configura | tion Index                                   |              |                |  |  |

|   | 7                                                   | 6       | 5 | 4 | 3         | 2                                            | 1            | 0              |  |  |

|   |                                                     |         |   |   |           |                                              |              | Default: 02H   |  |  |

| 1 | it 7 = Soft Re<br>= Reset Sta<br>= End Rese         | te      |   |   | May Be Wr | Configuration itten with Value Configuration | ues 1-4, Ref | er to Index in |  |  |

|   | it 6 = Level F<br>riven Low                         | Request |   |   |           |                                              |              |                |  |  |

# Table 5. Card Configuration and Status Register - PCMCIA (Global Power-Down Register)

|   |                                                     |             | (6          | liobal Power | -Down Regi | sier) |   |              |  |  |

|---|-----------------------------------------------------|-------------|-------------|--------------|------------|-------|---|--------------|--|--|

|   | Attribute Memory Plane Address: 4002H<br>Read/Write |             |             |              |            |       |   |              |  |  |

|   | Reserved PWRDWN Reserved                            |             |             |              |            |       |   |              |  |  |

|   | 7                                                   | 6           | 5           | 4            | 3          | 2     | 1 | 0            |  |  |

| В | it 2 = Power-<br>1 = 28F<br>0 = Pov                 | 016SAs in R | eset Power- | Down         |            |       |   | Default: 00H |  |  |

# Table 6. Card Status Register - Intel

|                                                                                                 |                         |                             | Attribut      | •    | ane Address:<br>d Only                              | 4100H               |      |                 |  |

|-------------------------------------------------------------------------------------------------|-------------------------|-----------------------------|---------------|------|-----------------------------------------------------|---------------------|------|-----------------|--|

|                                                                                                 | Rese                    | erved                       | SRESET        | CMWP | PWRDWN                                              | CISWP               | WP   | RDY/BSY#        |  |

|                                                                                                 | 7 6                     |                             | 5             | 4    | 3                                                   | 2                   | 1    | 0               |  |

|                                                                                                 |                         |                             |               |      |                                                     |                     | Defa | ult: 01H or 03H |  |

| Bit 5 = Soft Reset 1 = Reset State  Bit 2 = Common Memory CIS Write Protect 1 = Write Protected |                         |                             |               |      |                                                     |                     |      |                 |  |

| Bi                                                                                              |                         | on Memory W<br>te Protected | /rite Protect |      | Bit 1 = Write Protect Switch<br>1 = Write Protected |                     |      |                 |  |

| Ві                                                                                              | t 3 = Power-<br>1 = Pov | Down<br>wer-Down            |               |      |                                                     | Ready/Busy<br>Ready | /#   |                 |  |

|                                                                                                 |                         |                             |               |      |                                                     |                     |      |                 |  |

Table 7. Write Protection Register - Intel

|                 |  | Attribut |  | ane Address:<br>/Write | 4104H |      |       |  |

|-----------------|--|----------|--|------------------------|-------|------|-------|--|

|                 |  | Reserved |  |                        | BLKEN | CMWP | CISWP |  |

| 7 6 5 4 3 2 1 0 |  |          |  |                        |       |      |       |  |

Default: 04H

Bit 2 = Block Locking Enable

1 = Enable Independent 28F016SA Block Locking

0 = All Blocks Unlocked

Bit 1 = Common Memory Write Protect

1 = Common Memory Minus the CMCIS in Write Protect Status

0 = Write Protect According to Independent 28F016SA Block Locking Bit 0 = Common Memory CIS Write Protect

1 = Common Memory CIS in Write Protect Status

0 = Write Protect According to Independent 28F016SA Block Locking

## Table 8. Voltage Control Register - Intel

Attribute Memory Plane Address: 410CH Read/Write

| V <sub>CC</sub><br>LEVEL |   |   | Reserved |   |   | V <sub>PP</sub><br>VALID | V <sub>PP</sub><br>GEN |

|--------------------------|---|---|----------|---|---|--------------------------|------------------------|

| 7                        | 6 | 5 | 4        | 3 | 2 | 1                        | 0                      |

Default: 82 or 02H

Bit  $7 = V_{CC}$  Level: Read Only Bit

1 = Host Supplying 3.3V

0 = Host Supplying 5V

Bit 0 = V<sub>PP</sub> Generation

1 = Turn on Integrated V<sub>PP</sub> Generator

$0 = Turn off Integrated V_{PP} Generator$

Bit  $1 = V_{PP}$  Valid

$1 = V_{PP}$  between 11.4V and 12V

$0 = V_{PP}$  Invalid

**Note:** The  $V_{PP}$  Valid bit only reflects the state of the  $V_{PP}$  Generator, NOT the external  $V_{PP}$ .

## Table 9. Ready/Busy Mode Register - Intel

Attribute Memory Plane Address: 4140H

|   |   |      | Read  | /vvrite |   |      |      |

|---|---|------|-------|---------|---|------|------|

|   |   | Rese | erved |         |   | RACK | MODE |

| 7 | 6 | 5    | 4     | 3       | 2 | 1    | 0    |

Default: 00H

Bit 1 = Ready Acknowledge

0 = Clear RDY/BSY#

Bit 0 = RDY/BSY# Mode

1 = High-Performance Mode

0 = PCMCIA Level Mode

# 4.0 DEVICE COMMAND SET

The 28F016SA/DD28F032SA-based Series 2+Command Set increases functionality over earlier 28F008SA-based designs while maintaining backwards compatibility. The extended command set incorporates many new features to improve programmability and write performance such as: page buffered writing, individual block locking, multiple RDY/BSY# configurations and device level queuing capabilities. The following pages list the Series 2+ command set and Bus Cycle Operations overview.

Series 2+ Command Set

| Codes (H) | Series 2 Compatible Mode |

|-----------|--------------------------|

| 00H       | Invalid/Reserved         |

| 10H       | Alternate Data Write     |

| 20H       | Single Block Erase       |

| 40H       | Data Write               |

| 50H       | Clear Status Registers   |

| 70H       | Read CSR                 |

| 90H       | Read ID Codes            |

| ВОН       | Erase Suspend            |

| D0H       | Confirm/Resume           |

| FFH       | Read Flash Array         |

| Codes (H) | Series 2+ Performance<br>Enhancement |  |  |  |

|-----------|--------------------------------------|--|--|--|

| 0CH       | Page Buffer Write to Flash           |  |  |  |

| 71H       | Read GSR or BSRs                     |  |  |  |

| 72H       | Page Buffer Swap                     |  |  |  |

| 74H       | Single Load to Page Buffer           |  |  |  |

| 75H       | Read Page Buffer                     |  |  |  |

| 77H       | Lock Block                           |  |  |  |

| 80H       | Abort                                |  |  |  |

| 96H,01H   | RY/BY# Level Mode Enable             |  |  |  |

| 96H,02H   | RY/BY# Pulse-On-Write                |  |  |  |

| 96H,03H   | RY/BY# Pulse-On Erase                |  |  |  |

| 96H,04H   | RY/BY# Disable                       |  |  |  |

| 97H       | Upload Status Bits                   |  |  |  |

| 99H       | Upload Device Information            |  |  |  |

| A7H       | Erase All Unlocked Blocks            |  |  |  |

| E0H       | Sequential Load to Page Buffer       |  |  |  |

| F0H       | Sleep                                |  |  |  |

Table 10. 28F008SA-Compatible Mode Command Bus Definitions

|                               | First Bus Cycle |      |           |       |     | Second I | Bus Cycle | е     |

|-------------------------------|-----------------|------|-----------|-------|-----|----------|-----------|-------|

| Command                       | R/W             | Addr | Addr Data |       | R/W | Addr     | Da        | ata   |

|                               |                 |      | Byte      | Word  |     |          | Byte      | Word  |

| Read Array                    | W               | DA   | FFH       | FFFFH | R   | DA       | AD        | AD    |

| Intelligent Identifier        | W               | DA   | 90H       | 9090H | R   | IA       | ID        | ID    |

| Read CSR (See 1)              | W               | DA   | 70H       | 7070H | R   | DA       | CSRD      | CSRD  |

| Clear Status Register (See 2) | W               | DA   | 50H       | 5050H |     |          |           |       |

| Word/Byte Write §             | W               | WA   | 40H       | 4040H | W   | WA       | WD        | WD    |

| Word/Byte Write (Alternate) § | W               | WA   | 10H       | 1010H | W   | WA       | WD        | WD    |

| Block Erase/Confirm §         | W               | ВА   | 20H       | 2020H | W   | ВА       | D0H       | D0D0H |

| Erase Suspend/Resume          | W               | DA   | ВОН       | вовон | W   | DA       | D0H       | D0D0H |

ADDRESSES: DATA:

DA Device Address ΑD Array Data BA **Block Address CSRD** CSR Data Identifier Address ID **Identifier Data** IΑ WA Write Address WD Write Data

§ = Queueable Commands

- 1. The CSR is automatically available after the device enters Data Write, Erase or Suspend operations.

- 2. Clears CSR.3, CSR.4 and CSR.5. Also clears GSR.5 and all BSR.5 and BSR.2 bits.

# **SERIES 2+ FLASH MEMORY CARDS**

Table 11. 28F016SA-Super-Set Mode Performance Enhancement Command Bus Definitions

|                                               |       |      |      | us Cyc |       |      | Second         |      | cle    |      | Third B |      |      |

|-----------------------------------------------|-------|------|------|--------|-------|------|----------------|------|--------|------|---------|------|------|

| Command                                       | Notes | Oper | Addr |        | ata   | Oper | Addr           | Г    | ata    | Oper | Addr    | Da   | ata  |

|                                               |       |      |      | Byte   | Word  |      |                | Byte | Word   |      |         | Byte | Word |

| Read Page<br>Buffer                           |       | W    | DA   | 75H    | 7575H | R    | PA             | PD   | PDPD   |      |         |      |      |

| Page Buffer<br>Swap                           | 6     | W    | DA   | 72H    | 7272H |      |                |      |        |      |         |      |      |

| Single Load to<br>Page Buffer                 |       | W    | DA   | 74H    | 7474H | W    | PA             | PD   | PDPD   |      |         |      |      |

| Sequential<br>Load to Page<br>Buffer          | 4,5   | W    | DA   | E0H    | E0E0H | W    | DA             | E    | ЗСН    | W    | DA      | В    | CH   |

| Page Buffer<br>Write to Flash<br>Array §      | 3,4,5 | W    | DA   | 0CH    | 0C0CH | W    | A <sub>0</sub> | ВС   | C(L,H) | W    | WA      | BC(  | H,L) |

| RY/BY# Pulse-<br>On-Erase §                   | 7     | W    | DA   | 96H    | 9696H | W    | DA             | D0H  | D0D0H  |      |         |      |      |

| RY/BY# Pulse-<br>On-Write §                   | 7     | W    | DA   | 96H    | 9696H | W    | DA             | D1H  | D1D1H  |      |         |      |      |

| RY/BY# Enable<br>to Level-Mode<br>§           | 7     | W    | DA   | 96H    | 9696H | W    | DA             | D2H  | D2D2H  |      |         |      |      |

| RY/BY#<br>Disable §                           | 7     | W    | DA   | 96H    | 9696H | W    | DA             | D3H  | D3D3H  |      |         |      |      |

| Lock Block/<br>Confirm §                      |       | W    | DA   | 77H    | 7777H | W    | ВА             | D0H  | D0D0H  |      |         |      |      |

| Upload Status<br>Bits/<br>Confirm §           | 2     | W    | DA   | 97H    | 9797H | W    | DA             | D0H  | D0D0H  |      |         |      |      |

| Read Extended<br>Status<br>Registers          | 1     | W    | DA   | 71H    | 7171H | R    | RA             | GSRI | D/BSRD |      |         |      |      |

| Erase All<br>Unlocked<br>Blocks/<br>Confirm § |       | W    | DA   | A7H    | A7A7H | W    | DA             | D0H  | D0D0H  |      |         |      |      |

| Sleep                                         |       | W    | DA   | F0H    | F0F0H |      |                |      |        |      |         |      |      |

| Abort                                         |       | W    | DA   | 80H    | 8080H |      |                |      |        |      |         |      |      |

| Upload Device<br>Information                  |       | W    | DA   | 99H    | 9999H | W    | DA             | D0H  | D0D0H  |      |         |      |      |

#### SERIES 2+ FLASH MEMORY CARDS

| ADDRESS | ES                        | DATA   |                  | DATA COU | DATA COUNTS            |  |  |  |

|---------|---------------------------|--------|------------------|----------|------------------------|--|--|--|

| DA      | Device Address            | AD     | Write Address    | WC(L,H)  | Word Count (Low, High) |  |  |  |

| BA      | Block Address             | CSRD   | CSR Data         | BC(L,H)  | Byte Count (Low, High) |  |  |  |

| IA      | Identifier Address        | G/BSRD | GSR/BSR Data     | WD(L,H)V | Write Data (Low, High) |  |  |  |

| PA      | Page Buffer Address       | ID     | Identifier Data  |          |                        |  |  |  |

| RA      | Extended Register Address | WD     | Write Data       |          |                        |  |  |  |

| WA      | Write Address             | PD     | Page Buffer Data |          |                        |  |  |  |

| X       | Don't Care                |        |                  |          |                        |  |  |  |

§ = Queueable Commands

#### NOTES:

- 1. RA can be the GSR address or any BSR address.

- Upon device power-up, all BSR lock-bits are locked. The Lock Status Upload command must be written to reflect the actual lock-bit status.

- 3. A<sub>0</sub> is automatically complemented to load the second byte of data.

- BCH/WCH must be at 00H for this product because of the 256-byte Page Buffer size and to avoid writing the Page Buffer contents into more than one 256-byte segment within an array block. They are simply shown for Page Buffer expandability.

- 5. PA and PD (whose count is given in cycles 2 and 3) are supplied starting in the fourth cycle (not shown).

- 6. This command allows the user to swap between available page buffers (0 or 1).

- 7. These commands reconfigure RY/BY# output to one of two pulse modes, or they enable and disable the RY/BY# function.

## **5.0 DEVICE STATUS REGISTER**

Each 28F016SA has three types of status registers: the Compatible Status Register (CSR), the Global Status Register (GSR) and the Block Status Register (BSR). The Compatible Status Register is identical to the 28F008SA Status Register. The Global Status

Register contains queue and page buffer information about each device. Each block within the device has a Block Status Register assigned to it. The Block Status Register contains the Block Locking Status and other information specific to the block being addressed.

Table 12. Compatible Status Register

|      |     |    | Read Onl | y Register |   |          |           |

|------|-----|----|----------|------------|---|----------|-----------|

| WSMS | ESS | ES | DWS      | VPPS       |   | Reserved |           |

| 7    | 6   | 5  | 4        | 3          | 2 | 1        | 0         |

|      |     |    |          |            |   |          | D ( 1: 00 |

|    | 7                                          | 6                                              | 5                               | 4   | 3              | 2                                                            | 1                 | 0           |   |

|----|--------------------------------------------|------------------------------------------------|---------------------------------|-----|----------------|--------------------------------------------------------------|-------------------|-------------|---|

| -  |                                            |                                                |                                 |     |                |                                                              |                   | Default: 80 | Н |

| CS | SR.7 = WRIT<br>(WSMS<br>1 = Rea<br>0 = Bus | i)<br>ady                                      | ACHINE STA                      | TUS | 1 = E<br>0 = E | TA-WRITE S<br>Fror in Data \<br>Data Write Su<br>P STATUS (\ | Write<br>ccessful | S)          |   |

| CS | 1 = Era:                                   | se Suspende                                    | D STATUS (E<br>d<br>s/Completed | ,   | 1 = \          | / <sub>PP</sub> Low Dete<br>/ <sub>PP</sub> OK               |                   | Abort       |   |

| CS | 1 = Erro                                   | SE STATUS (<br>or In Block Er<br>cessful Block | asure                           |     |                |                                                              |                   |             |   |

Table 13. Global Status Register

| WSMS | ESS | ES | DWS | VPPS |   | Reserved |   |

|------|-----|----|-----|------|---|----------|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1        | 0 |

Default: 80H

CSR.7 = WRITE STATE MACHINE STATUS

(WSMS)

1 = Ready 0 = Busy

CSR.6 = ERASE-SUSPEND STATUS (ESS)

1 = Erase Suspended

0 = Erase In Progress/Completed

CSR.5 = ERASE STATUS (ES)

1 = Error In Block Erasure

0 = Successful Block Erase

CSR.4 = DATA-WRITE STATUS (DWS)

1 = Error in Data Write

0 = Data Write Successful

$CSR.3 = V_{PP} STATUS (VPPS)$

1 = V<sub>PP</sub> Low Detect, Operation Abort

$0 = V_{PP} OK$

#### Table 14. Block Status Register

| BS | BLS | BOS | BOAS | QS | VPPS | Rese | erved     |

|----|-----|-----|------|----|------|------|-----------|

| 7  | 6   | 5   | 4    | 3  | 2    | 1    | 0         |

|    |     |     |      |    |      |      | D-414- 00 |

Default: 80H

BSR.7 = BLOCK STATUS (BS)

1 = Ready

0 = Busy

BSR.6 = BLOCK-LOCK STATUS (BLS)

1 = Block Unlocked for Write/Erase

0 = Block Locked for Write/Erase

BSR.5 = BLOCK OPERATION STATUS (BOS)

1 = Operation Unsuccessful

0 = Operation Successful or

Currently Running

BSR.4 = BLOCK OPERATION ABORT STATUS (BOAS)

1 = Operation Aborted

0 = Operation Not Aborted

BSR.3 = QUEUE STATUS (QS)

1 = Queue Full

0 = Queue Available

BSR.2 = V<sub>PP</sub> STATUS (VPPS)

$1 = V_{PP}$  Low Detect, Operation Abort

$0 = V_{PP} OK$

# 6.0 PCMCIA CARD INFORMATION STRUCTURE

The Card Information Structure (CIS) begins at address 00000000H of the card's Attribute Memory Plane. It contains a variable length chain of data blocks (tuples) that conform to a basic format (Table 15). The CIS of the Series 2+ Flash Memory Card is found in Table 16.

#### **Table 15. PCMCIA Tuple Format**

| Bytes | Data                                                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Tuple Code: CISTPL_xxx. The tuple code 0FFH indicates no more tuples in the list.                                                                                                                                                                                    |

| 1     | Tuple Link: TPL_LINK. Link to the next tuple in the list. This can be viewed as the number of additional bytes in tuple, excluding this byte. A link field of zero indicates an empty tuple body. A link field containing 0FFH indicates the last tuple in the list. |

| 2-n   | Bytes specific to this tuple.                                                                                                                                                                                                                                        |

Table 16. Tuples for Series 2+ Card

| Address | Value | Description                          |  |  |  |  |

|---------|-------|--------------------------------------|--|--|--|--|

| 00h     | 01H   | CISTPL_DEVICE                        |  |  |  |  |

| 02h     | 04H   | TPL_LINK                             |  |  |  |  |

| 04h     | 57H   | FLASH                                |  |  |  |  |

| 06h     | 22H   | 150 ns                               |  |  |  |  |

|         | 32H   | 250 nx                               |  |  |  |  |

|         |       | CARD SIZE                            |  |  |  |  |

| 08h     | 0EH   | 4 MB                                 |  |  |  |  |

|         | 1EH   | 8 MB                                 |  |  |  |  |

|         | 4EH   | 20 MB                                |  |  |  |  |

|         | 9EH   | 40 MB                                |  |  |  |  |

| 0AH     | FFH   | END OF DEVICE                        |  |  |  |  |

| 0CH     | 1CH   | CISTPL_DEVICE_OC                     |  |  |  |  |

| 0EH     | 05H   | TPL_LINK                             |  |  |  |  |

| 10H     | 02H   | OTHER CONDITIONS - 3 V <sub>CC</sub> |  |  |  |  |

| 12H     | 57H   | FLASH                                |  |  |  |  |

| 14H     | 32H   | 250 ns                               |  |  |  |  |

|         |       | CARD SIZE                            |  |  |  |  |

| 16H     | 0EH   | 4 MB                                 |  |  |  |  |

|         | 1EH   | 8 MB                                 |  |  |  |  |

|         | 4EH   | 20 MB                                |  |  |  |  |

|         | 9EH   | 40 MB                                |  |  |  |  |

| 18H     | FFH   | END OF DEVICE                        |  |  |  |  |

| 1AH     | 17H   | CISTPL_DEVICE_A                      |  |  |  |  |

| 1CH     | 04H   | TPL_LINK                             |  |  |  |  |

| 1EH     | 1FH   | ROM                                  |  |  |  |  |

| 20H     | 22H   | 150 ns                               |  |  |  |  |

| 22H     | 01H   | 2 Kb                                 |  |  |  |  |

| 24H     | FFH   | END OF DEVICE                        |  |  |  |  |

| 26H     | 1DH   | CISTPL_DEVICE_OA                     |  |  |  |  |

| 28H     | 05H   | TPL_LINK                             |  |  |  |  |

| 2AH     | 02H   | OTHER CONDITIONS - 3 $V_{\rm CC}$    |  |  |  |  |

| 2CH     | 17H   | ROM                                  |  |  |  |  |

| 2EH     | 32H   | 250 ns                               |  |  |  |  |

| 30H     | 01H   | 2 Kb                                 |  |  |  |  |

| 32H     | FFH   | END OF DEVICE                        |  |  |  |  |

| 34H     | 18H   | CISTPL JEDEC_C                       |  |  |  |  |

| 36H     | 02H   | TPL_LINK                             |  |  |  |  |

| 38H     | 89H   | INTEL J-ID                           |  |  |  |  |

| or Series 2+ Card |       |                    |  |  |  |  |  |  |

|-------------------|-------|--------------------|--|--|--|--|--|--|

| Address           | Value | Description        |  |  |  |  |  |  |

| 3AH               | A0H   | 28F016 J-ID        |  |  |  |  |  |  |

| 3CH               | 00H   | NULL CONTROL TUPLE |  |  |  |  |  |  |

| 3EH               | 15H   | CISTPL VERS 1      |  |  |  |  |  |  |

| 40H               | 39H   | TPL_LINK           |  |  |  |  |  |  |

| 42H               | 04H   | TPLLV1_MAJOR       |  |  |  |  |  |  |

| 44H               | 01H   | TPLLV1_MINOR       |  |  |  |  |  |  |

|                   |       | TPLLV1_INFO        |  |  |  |  |  |  |

| 46H               | 49H   | I                  |  |  |  |  |  |  |

| 48H               | 6EH   | n                  |  |  |  |  |  |  |

| 4AH               | 74H   | t                  |  |  |  |  |  |  |

| 4CH               | 65H   | е                  |  |  |  |  |  |  |

| 4EH               | 6CH   | I                  |  |  |  |  |  |  |

| 50H               | 00H   | END TEXT           |  |  |  |  |  |  |

| 52H               | 53H   | S                  |  |  |  |  |  |  |

| 54H               | 32H   | 2                  |  |  |  |  |  |  |

| 56H               | 45H   | ш                  |  |  |  |  |  |  |

| 58H               | 34H   | 4 MB               |  |  |  |  |  |  |

|                   | 38H   | 8 MB               |  |  |  |  |  |  |

|                   | 32H   | 20 MB              |  |  |  |  |  |  |

|                   | 34H   | 40 MB              |  |  |  |  |  |  |

| 5AH               | 20H   | 4 MB               |  |  |  |  |  |  |

|                   | 20H   | 8 MB               |  |  |  |  |  |  |

|                   | 30H   | 20 MB              |  |  |  |  |  |  |

|                   | 30H   | 40 MB              |  |  |  |  |  |  |

| 5CH               | 53H   | S                  |  |  |  |  |  |  |

|                   | 20H   | SPACE              |  |  |  |  |  |  |

| 5EH               | 57H   | W                  |  |  |  |  |  |  |

|                   | 20H   | SPACE              |  |  |  |  |  |  |

| 60H               | 00H   | ENDTEXT            |  |  |  |  |  |  |

| 62H               | 43H   | С                  |  |  |  |  |  |  |

| 64H               | 4FH   | 0                  |  |  |  |  |  |  |

| 66H               | 50H   | Р                  |  |  |  |  |  |  |

| 68H               | 59H   | Υ                  |  |  |  |  |  |  |

| 6AH               | 52H   | R                  |  |  |  |  |  |  |

| 6CH               | 49H   | I                  |  |  |  |  |  |  |

| 6EH               | 47H   | G                  |  |  |  |  |  |  |

| 70H               | 48H   | Н                  |  |  |  |  |  |  |

| 72H               | 54H   | Т                  |  |  |  |  |  |  |

|                   |       |                    |  |  |  |  |  |  |

Table 16. Tuples for Series 2+ Card (Contd.)

| Address | Value | Description | Address | Value | Description                     |

|---------|-------|-------------|---------|-------|---------------------------------|

| 74H     | 20H   | SPACE       | BEH     | 40H   | TPCC_RADR                       |

| 76H     | 49H   | I           | C0H     | 03H   | TPCC_RMSK                       |

| 78H     | 6EH   | n           | C2H     | 00H   | NULL CONTROL TUPLE              |

| 7AH     | 74H   | t           | C4H     | 1BH   | CISTPL_CFTABLE_ENTRY            |

| 7CH     | 65H   | е           | C6H     | 08H   | TPL_LINK                        |

| 7EH     | 6CH   | I           | C8H     | 01H   | TPCE_INDEX (01H)                |

| 80H     | 20H   | SPACE       | CAH     | 01H   | TPCE_FS (V <sub>CC</sub> ONLY)  |

| 82H     | 43H   | С           |         |       | TPCE_PD                         |

| 84H     | 4FH   | 0           | CCH     | 79H   | V <sub>CC</sub> PARAMETER       |

| 86H     | 52H   | R           |         |       | SELECTION BYTE                  |

| 88H     | 50H   | Р           | CEH     | 55H   | V <sub>CC</sub> NOMINAL VOLTAGE |

| 8AH     | 4FH   | 0           |         |       | $5V \pm 5\%$                    |

| 8CH     | 52H   | R           | D0H     | 53H   | I <sub>CC</sub> STATIC 500 μA   |

| 8EH     | 41H   | Α           | D2H     | 1EH   | I <sub>CC</sub> AVERAGE 150 mA  |

| 90H     | 54H   | Т           | D4H     | 1EH   | I <sub>CC</sub> PEAK 150 mA     |

| 92H     | 49H   | I           | D6H     | 1BH   | I <sub>CC</sub> PWRDWN 200 μA   |

| 94H     | 4FH   | 0           | D8H     | 1BH   | CISTPL_CFTABLE_ENTRY            |

| 96H     | 4EH   | N           | DAH     | 0FH   | TPL_LINK                        |

| 98H     | 20H   | SPACE       | DCH     | 02H   | TPCE_INDEX (02H)                |

| 9AH     | 31H   | 1           | DEH     | 02H   | $TPCE\_FS\ (V_CC\ AND\ V_PP)$   |

| 9CH     | 39H   | 9           |         |       | TPCE_PD                         |

| 9EH     | 39H   | 9           | E0H     | 79H   | V <sub>CC</sub> PARAMETER       |

| A0H     | 33H   | 3           |         |       | SELECTION BYTE                  |

| A2H     | 20H   | SPACE       | E2H     | 55H   | V <sub>CC</sub> NOMINAL VOLTAGE |

| A4H     | 47H   | G           |         |       | $5V \pm 5\%$                    |

| A6H     | 4CH   | L           | E4H     | 2BH   | I <sub>CC</sub> STATIC 250 μA   |

| A8H     | 41H   | Α           | E6H     | 06H   | I <sub>CC</sub> AVERAGE 100 mA  |

| AAH     | 44H   | D           | E8H     | 06H   | I <sub>CC</sub> PEAK 100 mA     |

| ACH     | 45H   | E           | EAH     | 52H   | I <sub>CC</sub> PWRDWN 50 μA    |

| AEH     | 4BH   | K           |         |       | TPCE_PD                         |

| ВОН     | 00H   | END TEXT    | ECH     | 79H   | V <sub>PP</sub> PARAMETER       |

| B2H     | FFH   | END OF LIST |         |       | SELECTION BYTE                  |

| B4H     | 1AH   | CISTPL_CONF | EEH     | 8EH   | 12.0V ± 5%                      |

| В6Н     | 05H   | TUPL_LINK   | F0H     | 7DH   | NC OK ON STANDBY & PWD          |

| B8H     | 01H   | TPCC_SZ     | F2H     | 53H   | I <sub>PP</sub> STATIC 500 μA   |

| BAH     | 04H   | TPCC_LAST   | F4H     | 25H   | I <sub>PP</sub> AVERAGE 20 mA   |

| ВСН     | 00H   | TPCC_RADR   | F6H     | 25H   | I <sub>PP</sub> PEAK 20 mA      |

Table 16. Tuples for Series 2+ Card (Contd.)

|         |       | Table 10. Tuples 101           |

|---------|-------|--------------------------------|

| Address | Value | Description                    |

| F8H     | 52H   | IPP PWRDWN 50 μA               |

| FAH     | 1BH   | CISTPL_CFTABLE_ENTRY           |

| FCH     | 09H   | TPL_LINK                       |

| FEH     | 03H   | TPCE_INDEX (03H)               |

| 100H    | 01H   | TPCE_FS (V <sub>CC</sub> ONLY) |

|         |       | TPCE_PD                        |

| 102H    | 79H   | V <sub>CC</sub> PARAMETER      |

|         |       | SELECTION BYTE                 |

| 104H    | B5H   | $V_{CC} = 3.3V$                |

| 106H    | 1EH   | EXTENSION BYTE                 |

| 108H    | 04H   | I <sub>CC</sub> STATIC 1 mA    |

| 10AH    | 1EH   | I <sub>CC</sub> AVERAGE 150 mA |

| 10CH    | 1EH   | I <sub>CC</sub> PEAK 150 mA    |

| 10EH    | 53H   | I <sub>CC</sub> PWRDWN 500 µA  |

| 110H    | 1BH   | CISTPL_CFTABLE_ENTRY           |

| 112H    | 10H   | TPL_LINK                       |

| 114H    | 04H   | TPCE_INDEX (04H)               |

| 116H    | 02H   | TPCE_FS (VCC AND VPP)          |

|         |       | TPCE_PD                        |

| 118H    | 79H   | V <sub>CC</sub> PARAMETER      |

|         |       | SELECTION BYTE                 |

| 11AH    | B5H   | $V_{CC} = 3.3V$                |

| 11CH    | 1EH   | EXTENSION BYTE                 |

| 11EH    | 2BH   | I <sub>CC</sub> STATIC 250 μA  |

| 120H    | 06H   | I <sub>CC</sub> AVERAGE 100 mA |

| 122H    | 06H   | I <sub>CC</sub> PEAK 100 mA    |

| 124H    | 52H   | I <sub>CC</sub> PWRDWN 50 μA   |

|         |       | TPCE_PD                        |

| 126H    | 79H   | V <sub>PP</sub> PARAMETER      |

|         |       | SELECTION BYTE                 |

| 128H    | 8EH   | 12.0V =/- 5%                   |

| 12AH    | 7DH   | NC OK ON STANDBY & PWD         |

| 12CH    | 53H   | I <sub>PP</sub> STATIC 500 μA  |

| 12EH    | 25H   | I <sub>PP</sub> AVERAGE 20 mA  |

| 130H    | 25H   | I <sub>PP</sub> PEAK 20 mA     |

| 132H    | 1BH   | I <sub>PP</sub> PWRDWN 150 μA  |

| 134H    | 00H   | NULL CONTROL TUPLE             |

| Address | Value | Description           |

|---------|-------|-----------------------|

| 136H    | 00H   | NULL CONTROL TUPLE    |

| 138H    | 1EH   | CISTPL DEVICEGEO      |

| 13AH    | 06H   | TPL_LINK              |

| 13CH    | 02H   | DGTPL_BUS             |

| 13EH    | 11H   | DGTPL_EBS             |

| 140H    | 01H   | DGTPL_RBS             |

| 142H    | 01H   | DGTPL_WBS             |

| 144H    | 01H   | DGTPL_PART = 1        |

| 146H    | 01H   | FLASH DEVICE          |

|         |       | INTERLEAVE            |

| 148H    | 20H   | CISTPL_MANFID         |

| 14AH    | 04H   | TPL_LINK (04H)        |

|         |       | TPLMID_MANF           |

| 14CH    | 89H   | LSB                   |

| 14EH    | 00H   | MSB                   |

| 150H    | 12H   | 4 MB - 150 ns         |

|         | 22H   | 8 MB - 150 ns         |

|         | 42H   | 20 MB - 150 ns        |

|         | 62H   | 40 MB - 150 ns        |

| 152H    | 84H   | TPLMID_CARD MSB       |

| 154H    | 21H   | CISTPL_FUNCID         |

| 156H    | 02H   | TPL_LINK              |

| 158H    | 01H   | TPLFID_FUNCTION       |

|         |       | (MEMORY)              |

| 15AH    | 00H   | TPLFID_SYSINIT (NONE) |

| 15CH    | FFH   | CISTPL_END            |

|         | 00H   | INVALID ADDRESS       |

|         | _     | (156H-1FEH)           |

# 7.0 SYSTEM DESIGN CONSIDERATIONS

# 7.1 Power Supply Decoupling

Flash memory power-switching characteristics require careful device decoupling. System designers are interested in three supply current issues: standby, active and transient current peaks which are produced by rising and falling edges of CE<sub>1</sub># and CE<sub>2</sub>#. The capacitive and inductive loads on the card and internal flash memory device pairs determine the magnitudes of these peaks.

Three-line control and proper decoupling capacitor selection suppress transient voltage peaks. Series 2+ cards contain on-card ceramic decoupling capacitors connected between  $V_{\rm CC}$  and GND, and between  $V_{\rm PP1}/V_{\rm PP2}$  and GND.

The card connector should also have a 4.7  $\mu$ F electrolytic capacitor between V<sub>CC</sub> and GND, as well as between V<sub>PP1</sub>/V<sub>PP2</sub> and GND. The bulk capacitors overcome voltage slumps caused by printed-circuit-board trace inductance, and supply charge to the smaller capacitors as needed.

#### 7.2 Power-Up/Down Protection

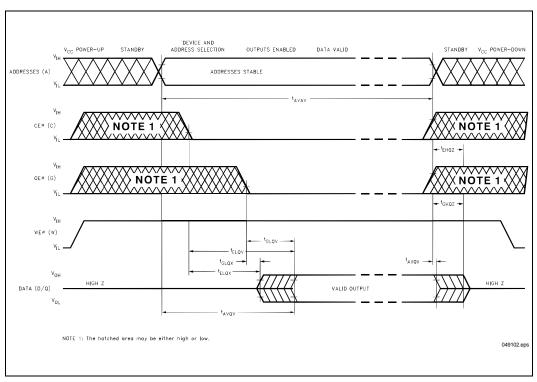

The PCMCIA/JEIDA-specified socket properly sequences the power supplies to the flash memory card via shorter and longer pins. This design assures that hot insertion and removal will not result in card damage or data loss.

Each device in the memory card is designed to offer protection against accidental erasure or writing, caused by spurious system-level signals that may exist during power transitions. The card will power-up into the read state.

A system designer must guard against active writes for  $V_{CC}$  voltages above  $V_{LKO}$  when  $V_{PP}$  is active. Since both WE# and CE1# must be low for a command write, driving either to  $V_{IH}$  will inhibit writes. With its control register architecture, alteration of device contents only occurs after successful completion of the two-step command sequences. While these precautions are sufficient for most applications, an alternative approach would allow  $V_{CC}$  to reach its steady state value before raising  $V_{PP1}/V_{PP2}$  above  $V_{CC}$  + 2.0V. In addition, upon powering down,  $V_{PP1}/V_{PP2}$  should be below  $V_{CC}$  + 2.0V before lowering  $V_{CC}$ .

#### NOTE

The Integrated  $V_{PP}$  generator defaults to the power off condition after reset and system power-up. The Vpp Generation circuitry must be enabled for the memory card to operate in 3.3V-Only or 5.0V-Only mode.

#### 7.3 Hot Insertion/Removal

The capability to remove or insert PC cards while the system is powered on (i.e., hot insertion/removal) requires careful design approaches on the system and card levels. To design for this capability, consider card over-voltage stress, system power fluxuations and control line stability.

## 8.0 ELECTRICAL SPECIFICATIONS

# 8.1 Absolute Maximum Ratings\*

NOTICE: This is a production datasheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

- 1. Operating temperature is for commercial product defined by this specification.

- 2. Minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to 2.0V for periods less than 20 ns. Maximum DC voltage on output pins is  $V_{CC}$  +0.5V, which may overshoot to  $V_{CC}$  + 2.0V for periods less than 20 ns.

- 3. Maximum DC input voltage on V<sub>PP1</sub>/V<sub>PP2</sub> may overshoot to +14.0V for periods less than 20 ns.

- 4. V<sub>PP</sub> generator turned "on" for 3.3V or 5.0V only operation.

| Symbol                                                    | Parameter                               | Min  | Max  | Units |

|-----------------------------------------------------------|-----------------------------------------|------|------|-------|

| V <sub>CC</sub> at 3.3V, 12V V <sub>pp</sub>              | V <sub>CC</sub> Supply Voltage (±0.3V)  | 3.0  | 3.6  | V     |

| V <sub>CC</sub> at 3.3V, V <sub>PP</sub> Gen <sup>4</sup> | V <sub>CC</sub> Supply Voltage (±0.15V) | 3.15 | 3.45 | V     |

| V <sub>CC</sub> at 5.0V                                   | V <sub>CC</sub> Supply Voltage (±0.25V) | 4.75 | 5.25 | V     |

# 9.0 SERIES 2+ DC CHARACTERISTICS

# 9.1 General

| Symbol             | Parameter                                       | Notes | Min                   | Max                   | Units | Test Conditions                          |

|--------------------|-------------------------------------------------|-------|-----------------------|-----------------------|-------|------------------------------------------|

| ILI                | Input Leakage Current                           | 1,3   |                       | ±20                   | μΑ    | V <sub>CC</sub> = V <sub>CC</sub> Max    |

|                    |                                                 |       |                       |                       |       | $V_{IN} = V_{CC}$ or GND                 |

| I <sub>LO</sub>    | Output Leakage Current                          | 1     |                       | ±20                   | μΑ    | V <sub>CC</sub> = V <sub>CC</sub> Max    |

|                    |                                                 |       |                       |                       |       | V <sub>OUT</sub> =V <sub>CC</sub> or GND |

| $V_{\rm IL5}$      | Input Low Voltage                               | 1     | 0                     | 0.8                   | V     | V <sub>CC</sub> = 5V                     |