### **AP-361**

# APPLICATION NOTE

# Implementing the Integrated Registers of the Series 2 Flash Memory Card

MARKUS LEVY

SENIOR TECHNICAL APPLICATIONS ENGINEER

January 1996

Order Number: 292096-003

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1995

# IMPLEMENTING THE INTEGRATED REGISTERS OF THE SERIES 2 FLASH MEMORY CARD

| CONTENTS                                | PAGE | CONTENTS                   | PAGE |

|-----------------------------------------|------|----------------------------|------|

| INTRODUCTION                            |      | Ready-Busy Status Register | 6    |

|                                         |      | Ready-Busy Mask Register   |      |

| SERIES 2 COMPONENT MANAGEMENT REGISTERS | 0    | Ready-Busy Mode Register   |      |

|                                         |      | Write Protection Register  | 12   |

| PCMCIA Release 2.0 Defined              |      | Card Status Register       | 19   |

| Soft Reset Register                     | 2    | cara ciatac riegioter      |      |

| Global Reset-Powerdown Register         | 4    | SUMMARY                    | 14   |

| Performance Enhancement Register        | rs5  | GLOSSARY                   | 1!   |

| Sleep Control Register                  | 5    | <b>42007.111</b>           |      |

| 1 0                                     |      | RELATED DOCUMENTS          | 1.9  |

#### INTRODUCTION

Intel's first generation flash memory cards<sup>(1)</sup> forever changed the vision of solid-state storage. Electrically rewritable, non-volatile, reliable, yet economical in high densities, these cards provided a unique solution for the portable computing industry demanding such media. The second generation of flash memory cards provide even higher densities, lower power consumption and a higher level of functionality. The Series 2 Flash Memory Card delivers a major technology breakthrough by supporting densities up to 20 Mbytes<sup>(2)</sup>, an integrated memory control register set (Component Management Registers or CMRs) and PCMCIA 2.0 compliance.

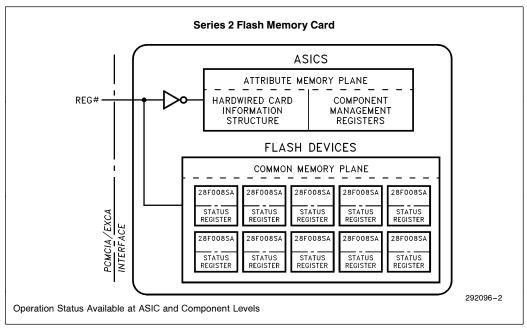

Intel's 8-Megabit FlashFile<sup>TM</sup> Memory, 28F008SA, provides the foundation for the Series 2 Flash Memory Card. Its properties include data-write and block-erase automation, sixteen 64 Kbyte, separately-erasable blocks, a Ready/Busy# output pin, and a Powerdown mode. Within the Series 2 Card, high-functionality

ASICs link the flash memory devices with the PCMCIA-specified electrical interface. These ASICs handle buffering, decoding and all control signals. They also contain the CMRs and hardwired Card Information Structure (CIS) used by system software to enhance device-level functions.

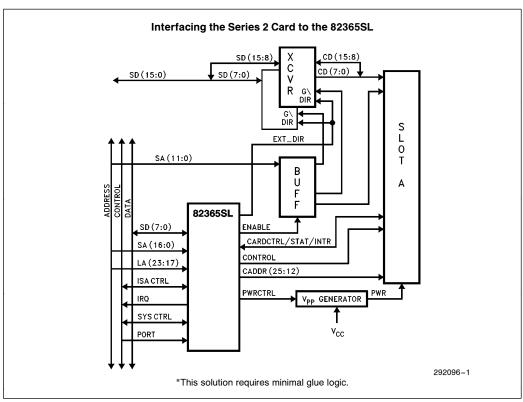

The OEM has many hardware and software alternatives for using the Series 2 Card. From a hardware perspective, the Intel 82365SL offers the most practical solution for controlling the PCMCIA socket in a PC solid-state drive application. This component, called the PC Card Interface Controller, provides the ExCA compliant hardware interface between the host system and the Series 2 Cards. As shown in Figure 1, the fundamental glue logic consists of a V<sub>PP</sub> generator and V<sub>CC</sub> control, a latching transceiver and address and decode signal buffers. Embedded systems can provide proper card signals with discrete circuitry.

Figure 1. The 82365SL Requires Minimal Glue Logic

#### NOTES:

- 1. The Bulk-Erase iMC001FLKA, iMC002FLKA, and iMC004FLKA (One, Two and Four Megabytes, respectively).

- 2. Higher density cards may be realized in the future as component densities go beyond 8 Megabits.

1

Figure 2. Selecting the Attribute or Common Memory Planes

Computer systems using the Series 2 Card as a solidstate disk drive employ file management software, such as Microsoft's\* Flash File System. This software capitalizes on the architectural benefits of flash memory. It includes drivers that interface directly to the Series 2 Card. Beyond specifying the hardware architecture, PCMCIA provides a software solution that consists of modular software pieces designed for easy adaptation to the various hardware platforms and memory technologies. The various pieces of the PCMCIA system may be obtained from your BIOS vendor. Essentially, this means that a system OEM is relieved of having to write any software for Series 2 Flash Memory Card.

This application note supplements the information contained in the Series 2 Flash Memory Card Data Sheet. It benefits OEMs developing their own Series 2 Flash Memory Card software pieces, including custom flash file management software and software for embedded systems running non-DOS applications. Specifically, it describes the software aspects of implementing the card's CMRs which provide software control of many 28F008SA functions, elevating the system designer above device-level issues used by higher-level file system software.

# SERIES 2 COMPONENT MANAGEMENT REGISTERS

The CMRs optimize the Series 2 Flash Memory Card's performance by supplying a software-controlled interface to the individual devices within the card. As shown in Figure 2, they are accessed as memory-mapped I/O in the Attribute Memory Plane by pulling the card's Register Select pin low (REG#, pin 61)(3). CMRs can be divided into two basic categories; those defined by the PCMCIA Release 2.0 specification and Intel defined "Performance Enhancement Registers".

#### **PCMCIA RELEASE 2.0 DEFINED**

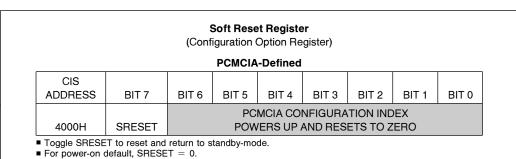

#### **Soft Reset Register**

(Configuration Option Register)

During card operation, it may be necessary to place the card into a known state by resetting the 28F008SA-level Status Registers and the CMRs in the ASICs to their power-on conditions (Figure 3). Specifically, in the

#### NOTE

3. No switch-over setup-time from Common Memory is needed when PCMCIA timing requirements are met.

#### Component Management Registers (4)

Defined by the PCMCIA R2.0 specification

- Soft Reset Register (5)—(R/W)

- Global Reset-Powerdown Register (6)—(R/W)

PERFORMANCE ENHANCEMENT REGISTERS designed to deliver control benefits tied directly to the Intel 28F008SA:

- Sleep Control Registers—(R/W)

- Ready-Busy Status Registers—(RO)

- Ready-Busy Mode Registers—(R/W)

- Ready-Busy Mask Registers—(R/W)

- Write Protection Registers—(R/W)

- Card Status Register—(RO)

ASICs, this reset affects the RP bit (Global Reset-Powerdown Register), the Sleep Control Register, the Ready-Busy Mode Register, the Ready-Busy Mask Register, and the CISWP and CMWP bits (Write Protection Register). There are several ways to enter power-on status:

- 1. Issuing a hardware reset, with a complete system reset or socket reset through the interface hardware, affects the entire system or the Series 2 Card, respectively.

- 2. During normal operation of many portable systems, tremendous power savings are realized by entering a suspend state. In this state, power to the card's socket is removed. After reapplying power, the card automatically attains its power-on status. Therefore, before removing power from the Series 2 Card, system software must save the contents of the Component Management Registers. It should also be pointed out, that a startup period must elapse to allow all internal circuitry to stabilize before accessing the card. This time period depends on host system power supply capabilities.(7)

- 3. The third method utilizes a software-controlled mechanism built into the Series 2 Card. This option, activated with the Soft Reset Register, provides a simple approach for placing the card in its power-on state without time delay.

The Soft Reset Register (Figure 4) contains a soft reset (SRESET) bit that performs a function similar to the hardware reset invoked by the card's RESET pin (RST#, pin 58)(8). Achieve the reset condition by issuing a two-step write sequence to the SRESET bit (i.e. toggling from 0 to 1 and back to 0).

During reset (SRESET = 1), the ASICs drive the flash memory array into the deep-sleep mode. This aborts any device operations in progress and resets each device's Status Register. After initiating a soft reset, the SRESET bit must be cleared (zero) to enable access to the flash memory array or write to another CMR. The host system can clear this bit by writing in a zero or issuing a hardware reset.

#### Power-On Conditions\*

ALL DEVICES IN STANDBY MODE. SOFTWARE WRITE-PROTECT DISABLED. ALL DEVICES' READY/BUSY# OUTPUTS UNMASKED. PCMCIA-READY/BUSY# MODE ENABLED. READY/BUSY# OUTPUT PIN GOES TO READY.

Generated by Hardware Reset or Toggling SRESET Bit.

#### Figure 3

#### NOTES:

- 4. R = READ, W = WRITE, RO = READ ONLY

- 5. Referred to as Configuration Option Register by PCMCIA R2.0.

- 6. Referred to as Configuration and Status Register by PCMCIA R2.0.

- 7. As specified by PCMCIA Release 2.0.

- 8. Soft reset puts all devices into power-down mode and requires a recovery time after returning from soft reset (500 ns for reads and 1  $\mu$ s for writes).

Figure 4. Useful for placing the card into a known state

The other two fields (not implemented with the Series 2 Card), defined in this register by the PCMCIA R2.0 specification, include the Configuration Index and the LevlREQ. After powerup or soft reset, the Configuration Index contains zeros to maintain compatibility as a Memory-Only Interface. The LevlREQ bit is hardwired

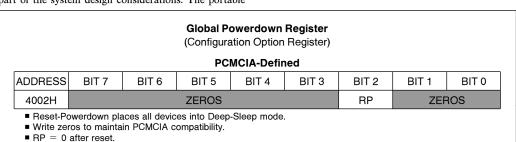

#### **GLOBAL RESET-POWERDOWN** REGISTER

#### **PCMCIA R2.0 Defined**

(Configuration and Status Register)

The portable system designer strives to minimize power consumption in every conceivable way. Solid-state storage devices using Intel Flash Memory deliver significant power consumption reductions (when compared to the mechanical disk) and therefore play an important part of the system design considerations. The portable system aimed at power conservation looks to shut down portions of system circuitry not in use (i.e. the solidstate drive not accessing files, the screen's backlight when the keyboard has not been touched in a certain amount of time, etc.). Powering down the entire socket achieves a minimal power usage status. However, the powerup recovery time from this approach produces varying delays.

The Series 2 Card offers the optimal solution with the Global Reset-Powerdown Register (Figure 5). Writing a one (1) to the Reset-PwrDwn Bit (RP bit 2) of this register puts all internal devices into the Deep-Sleep Mode by pulling every device's RP# input low<sup>(9)</sup>. In the Deep-Sleep mode, a 20 Megabyte Series 2 Card consumes 90% less current versus the standby mode current(10).

When the host system drives the two card enable pins high(11), the Series 2 ASIC circuitry blocks system-level address and data signals from the internal devices. Additionally, latching address buffers and data transceiv-

Figure 5

#### NOTES:

9. The remaining fields in this register (Changed, SigChg, IOis8, Audio, Intr and Rsvd) are tied low in the Series 2 Card for PCMCIA compatibility and for simplifying software masking.

10. I<sub>CCS</sub> = 30  $\mu$ A vs, I<sub>CCSL</sub> = 0.2  $\mu$ A; refer to 28F008SA Data Sheet. The ASICs consume 1  $\mu$ A. 11. CE1# (pin 7) and CE2# (pin 42) = V<sub>IH</sub>

#### SAMPLE 80X86 CODE TO HANDLE RECOVERY-PERIOD TIMING

GLOBAL RP 4002H ;Global Reset-PowerDown Register EQU

NOT\_RP EQU OH

MOV AX, MEM\_CARD\_BASE :Load card address

MOV ES, AX

MOV DI, GLOBAL\_RP ;Pointer setup

;Software assumes already in REG# mode access MOV BYTE PTR ES:[DI], NOT\_RP ;Clears RP bit

MOV CX, RECOVERY\_TIME ;Based on speed of processor

FOR\_A\_WHILE:

LOOP FOR\_A\_WHILE

Figure 6. Assembly Language Code for Returning from "Deep-Sleep" Mode

ers on the host side eliminate address and data signal switching at the Series 2 Card input buffers further reducing power consumption levels. In other words, to achieve the lowest power consumption levels, these signals should not be floated or tristated.

After clearing the RP bit, the device-recovery times must be met before accessing the flash memory. As shown in Figure 6, the recovery period can be implemented using a simple software algorithm(12).

Prior to entering the Reset-Powerdown Mode, your software must check operation status for data-writes or block-erases in progress(13). Any operations in progress will be terminated when powering down the flash array. The 28F008SA does not maintain Status Register contents in the Reset-Powerdown Mode. Therefore, when the card returns to standby mode, all devices will report successful status (Status Register = 80H) indicating the need for software drivers to use the reset-powerdown function intelligently.

#### PERFORMANCE ENCHANCEMENT **REGISTERS**

#### Sleep Control Register

(Performance Enhancement Register)

The reset-powerdown functionality of the Global Reset-Powerdown Register has a global affect on all devices. In many solid-state storage applications, reading or writing files only requires access to select device pairs and the remaining devices could be kept in Deep-Sleep status until needed.

| Sleep Control Registers Performance Enhancement Register |                  |                                                 |                  |                |                |                |                |                |  |  |

|----------------------------------------------------------|------------------|-------------------------------------------------|------------------|----------------|----------------|----------------|----------------|----------------|--|--|

| ADDRESS                                                  | BIT 7            | BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 |                  |                |                |                |                |                |  |  |

| 411AH                                                    |                  | DEVICES<br>18/19                                | DEVICES<br>16/17 |                |                |                |                |                |  |  |

| 4118H                                                    | DEVICES<br>14/15 | DEVICES<br>12/13                                | DEVICES<br>10/11 | DEVICES<br>8/9 | DEVICES<br>6/7 | DEVICES<br>4/5 | DEVICES<br>2/3 | DEVICES<br>0/1 |  |  |

- For reset, all devices powered up (bits = 0).

- On cards less than 20 megabytes, absent devices read as "0"s.

Bits cleared to zero by SRESET and RESET.

Figure 7. Allows Selective Reset-Powerdown of Devices within the Series 2 Card

12. PCMCIA does not specify a maximum recovery time. Recovery times, varying for different card technologies, must be handled on a case-by-case basis.

13. Polling the individual device's Status Register, the Ready/Busy Status Register, or the RDY/BSY# bit in the Card Status Register.

#### 28F008SA Status Register Bit Definition

| BIT 7         | BIT 6                      | BIT 5           | BIT 4           | BIT 3         | BIT 2 | BIT 1  | BIT 0 |

|---------------|----------------------------|-----------------|-----------------|---------------|-------|--------|-------|

| WSM<br>STATUS | ERASE<br>SUSPEND<br>STATUS | ERASE<br>STATUS | WRITE<br>STATUS | VPP<br>STATUS | R     | ESERVE | D     |

Figure 8. Read during Write or Erase Operations to Determine Status

The Sleep Control Register (Figure 7) offers this option; each bit provides power down for a specific device pair. Except for the global vs individual affect, this register functions identically to the Global Reset-Powerdown Register. The global reset-powerdown can be enabled while individual devices are sleeping. Disabling the global RESET-PWRDWN does not affect prior bit settings of the Sleep Control Register.

In many applications using the Series 2 Card, the card will be in the Standby Mode a large percentage of the time. This avoids device recovery times associated with complete socket power off or entering the Deep-Sleep Mode. In the Standby Mode, the Sleep Control Register offers the greatest advantage over the Global Reset-Powerdown Register. With the capability of controlling individual device pairs, a power savings improvement of approximately 16 times (based on typical current values) will be seen. This is derived from the following information:

- 28F008SA devices in Deep-Sleep;  $I_{CC}=0.2~\mu A$ ,  $I_{PP}=0.1~\mu A$ .

- 28F008SA devices in Standby;  $I_{CC} = 30 \mu A$ ,  $I_{PP} = 1 \mu A$ .

- ASICs in Standby and Sleep;  $I_{CC} = 1 \mu A$ .

- With device-pair control, unaccessed devices remain in Deep Sleep.

Although the other operating modes (read, data-write, or block-erase) also experience power savings by using the **Sleep Control Register**, the effects are not as significant relative to the higher current requirements of those modes.

When using the Sleep Control Register, software must account for the same device-recovery time of the global reset-powerdown method. To access files (or data) that span multiple device pairs (and experience uninterrupted access), software can perform a "look-ahead" function to determine which device pairs must be powered up.

#### **READY-BUSY STATUS REGISTER**

#### **Performance Enhancement Register**

The automated data-write and block-erase capability of the Intel 28F008SA FlashFile Memory results in a significant performance improvement. Furthermore, automation simplifies system-level interfacing as the user only delivers the proper command and monitors the operation's READY/BUSY status. Referring to the 28F008SA Data Sheet (or Figure 8), operation status can be obtained from the device's Status Register or RY/BY# pin. The device's Status Register allows software polling for ready status in addition to write and erase status. The RY/BY# pin can be used to generate an interrupt when making a busy to ready transition. Regardless of the method used for determining ready status, the Status Register should be read to determine whether an operation was successful.

In the Series 2 Card, where multiple devices are present and multiple simultaneous operations can occur, software polling each device's Status Register requires extra software and time. Furthermore, the PCMCIA interface only has one RDY/BSY# pin which obviously prevents 20 devices from hooking their individual RY/BY# out to the system. The ASICs within the card take these signals and feed them into the BUSY# Status Register (Figure 9). This facilitates multiple device-pair operations by allowing an analysis of all devices simultaneously. After initiating the data-write and block-erase operations, the system can switch the card to the Attribute Memory Plane to access these registers. Alternatively, each device's RY/BY# signal funnels into a single "wired or" signal that becomes the PCMCIA-RDY/BSY# pin driving an interrupt or polled through an I/O port.

When performing single device pair operations, Ready/Busy status should be accessed directly from the Status Register of the flash memory devices for the following reasons: 1) A device's Status Register must be read anyway to determine the result of an operation; 2) This saves several instructions required to switch to the Attribute Memory Plane.

#### **Ready-Busy Status Register**

Performance Enhancement Register

| CIS<br>ADDRESS | BIT 7    | BIT 6  | BIT 5  | BIT 4  | BIT 3        | BIT 2        | BIT 1        | BIT 0        |

|----------------|----------|--------|--------|--------|--------------|--------------|--------------|--------------|

| 4134H          | RESERVED |        |        |        | DEVICE<br>19 | DEVICE<br>18 | DEVICE<br>17 | DEVICE<br>16 |

| 4132H          | DEVICE   | DEVICE | DEVICE | DEVICE | DEVICE       | DEVICE       | DEVICE       | DEVICE       |

|                | 15       | 14     | 13     | 12     | 11           | 10           | 9            | 8            |

| 4130H          | DEVICE   | DEVICE | DEVICE | DEVICE | DEVICE       | DEVICE       | DEVICE       | DEVICE       |

|                | 7        | 6      | 5      | 4      | 3            | 2            | 1            | 0            |

- Each bit corresponds to a device's RY/BY# signal.

- Devices not present (i.e. < 20 Megabytes) return ready status.

Figure 9. Monitors Individual Device's RY/BY # Pins

#### **Example for Monitoring Ready/Busy Status**

```

(Assume ES contains memory card base address)

RDY_BSY_STATUS

EQU 4130H ;Register address

EQU 01H

DEVICE_O

;Settings in register for specific devices

DEVICE_1

EQU 02H

DEVICE_2

EQU 04H

DEVICE_3

EQU 08H

EQU 10H

DEVICE_4

EQU 20H

DEVICE_5

XOR AX, AX

;Zero AX Register

MOV DI, RDY_BSY_STATUS

;Insert code to start write operation in first 3 Device Pairs

;i.e. Devices 0, 1, 2, 3, 4, 5.

OR AX, DEVICE_O

OR AX, DEVICE_1

OR AX, DEVICE_2

OR AX, DEVICE_3

OR AX, DEVICE_4

OR AX, DEVICE_5

```

;Assume card already in REG mode.

TEST BYTE PTR ES:[DI], AX ;Zero flag cleared when programming ;devices are ready.

## READY-BUSY MASK REGISTER Performance Enhancement Register

As described earlier, completion of a data-write or block-erase operation can be determined by attaching the card's RDY/BSY# pin into a system interrupt. This frees the host system to perform alternate tasks after initiating an operation. In other words, device-level automation allows Series 2 Card operations to become background tasks.

Occasions exist where the interrupt generated from a device becoming ready produces unacceptable latency times. For instance, data-write operations, completing in only 10  $\mu$ s, realize a performance penalty dealing with interrupt latencies longer than the write time itself. The data-write operations would achieve a higher level of performance by using software polling techniques(14). On the other hand, block-erase operations typically require one second. Therefore, these opera-

tions perform well as background tasks because the interrupt latency constitutes a small fraction of the total time.

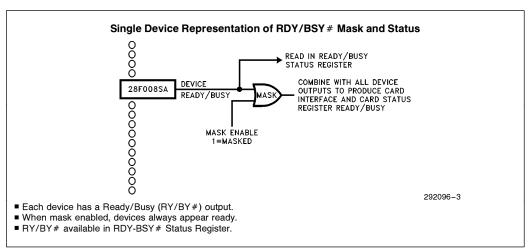

This discussion implies that the system interrupt should be disabled for data-writes and enabled for block-erases. What if an application requires simultaneous writes and erases? The Series 2 Flash Memory Card handles this situation with its Ready-Busy Mask Register (Figure 10). Setting the appropriate mask bits in the Ready-Busy Mask Register blocks the corresponding device's RY/BY# signals. With a device's mask bit set, the card's RDY/BSY# pin and Card Status Register (bit 0) always reflect a ready condition, regardless of the operation status. Figure 11 displays a conceptual mask circuit for a single device. The mask settings have no effect on the card's Ready-Busy-Status Registers (providing direct access to each device's RY/BY# output) or the Device Status Register. This allows software polling in the usual manner.

#### Ready-Busy Mask Register

Performance Enhancement Register

| CIS<br>ADDRESS | BIT 7    | BIT 6  | BIT 5  | BIT 4  | BIT 3        | BIT 2        | BIT 1        | BIT 0        |

|----------------|----------|--------|--------|--------|--------------|--------------|--------------|--------------|

| 4124H          | RESERVED |        |        |        | DEVICE<br>19 | DEVICE<br>18 | DEVICE<br>17 | DEVICE<br>16 |

| 4122H          | DEVICE   | DEVICE | DEVICE | DEVICE | DEVICE       | DEVICE       | DEVICE       | DEVICE       |

|                | 15       | 14     | 13     | 12     | 11           | 10           | 9            | 8            |

| 4120H          | DEVICE   | DEVICE | DEVICE | DEVICE | DEVICE       | DEVICE       | DEVICE       | DEVICE       |

|                | 7        | 6      | 5      | 4      | 3            | 2            | 1            | 0            |

1 = MASKED

Figure 10. Allows Masking of Individual Device's Ready/Busy Signals

#### Selecting the Appropriate Device to Mask

Assume the register set DI:DX contains a 32-bit physical address into SERIES 2 card. Each device pair represents 2 Megabytes (i.e. 200000H).

MOV CL, 5 ;Load shift count

SHR DI, CL ; Result in DI is device pair number to mask.

;Now determine whether to mask device pair for word operations or use Bit 0 of the DX portion to determine high or low device (odd or even) for byte operations.

#### NOTE:

14. Polling the individual device's Status Register, the Ready/Busy Status Register, or the RDY/BSY# bit in the Card Status Register.

Figure 11. The Ready-Busy Mask is Very Useful for Write Optimization

#### **READY-BUSY MODE REGISTER**

#### **Performance Enhancement Register**

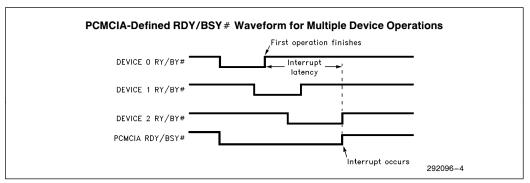

The PCMCIA specification for the Ready/Busy interface states that "the RDY/BSY# line is driven low by the memory card to indicate that the memory-card circuits are busy and unable to accept a data-transfer operation." Contrary to the PCMCIA specification, devicelevel data-write and block-erase automation enables the Series 2 Card to perform multiple operations simultaneously. Using the PCMCIA-specified method of RDY/BSY# functionality for multiple device operations, the RDY/BSY# interrupt does not notify the system until all devices finish because busy devices hold the RDY/BSY# signal low, as shown in Figure 12. Multiple block erases (typical block erase time of 1 second) could present an unacceptable pushout if system software waits for the first available "clean" block to write data.

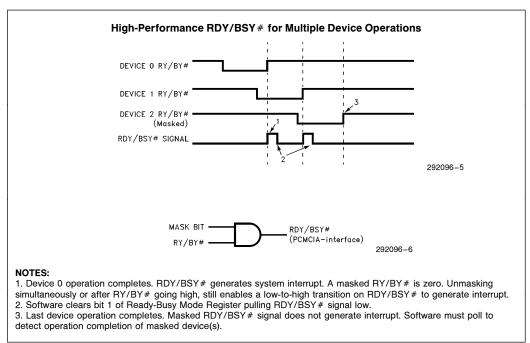

The Series 2 Card offers an alternative Ready/Busy mode (High-Performance Ready/Busy mode, alias "Levy"-mode) removing the performance impact of the PCMCIA mode. Circuitry internal to the ASIC catches every "READY-going" edge from each device. After an individual device becomes ready (Ready/Busy signal goes high), the system has the opportunity to immediately service the interrupt. System software must now toggle the CLEAR bit (bit 1) in the Ready-Busy Mode Register (Figure 14) to reactivate the Ready/Busy signal. Figure 13 demonstrates the resulting waveform.

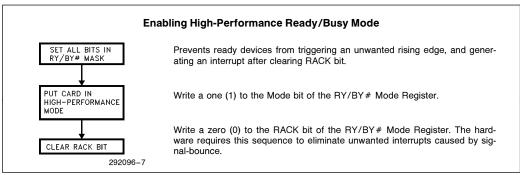

The Series 2 Card powers up in the PCMCIA-mode. Switching into the High Performance mode requires a two step process, as shown in Figure 15. ASIC circuitry design prevents being able to write a zero to the RACK bit on the same cycle as entering the High-Performance RDY/BSY Mode. This intentional design technique eliminates the possibility of receiving a noise generated RDY/BSY# rising edge, which would trigger an unwanted interrupt.

Figure 12. PCMCIA-Defined RDY/BSY Waveform for Multiple-Device Operations

Figure 13. High-Performance Mode Catches Each Device Going Ready

#### Ready/Busy Mode Register **Performance Enhancement Register**

| ADDRESS | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4140H   |       |       | RESE  | RVED  |       |       | RACK  | MODE  |

- Mode = Ready/Busy Mode 0 = PCMCIA Mode

- 1 = High-Performance Mode

- RACK = Ready Acknowledge Bit

- Clear this bit after receiving ready status to prepare for next device's ready transition

Register defaults to PCMCIA Mode for power on or reset. In PCMCIA Mode, RACK is a Don't Care

#### Figure 14. To Prevent Accidental Ready Transitions, a Three Step Sequence must be Followed to Enter High-Performance Mode

As discussed in the previous section, the block-erase operation benefits from the interrupt capabilities of the RDY/BSY# signal. However, if your software only erases one device pair at any time, the PCMCIA-RDY/ BSY # Mode will be sufficient for two reasons: 1) Both devices started simultaneously will complete the erase operation almost at the same time; 2) in 16-bit access mode, both devices of the pair must be erased before writing.

#### To block-erase in multiple devices:

- 1. Be sure to mask all devices (in Ready/Busy Mask Register).

- 2. If not already done, place the Series 2 Card in the High-Performance Mode (refer to Figure 15).

- 3. Issue the block-erase command sequence to the appropriate devices.

Figure 15. Entering High-Performance Mode

4. Unmask appropriate Ready-Busy Mask Register bits. The circuitry catches devices with already completed erase operations with the conceptual setup shown in Figure 13. Use a RAM-based variable or register for an erase-block queue to monitor erasing devices.

The interrupt service routine (ISR) can be as simple as removing the erase block from the queue. It could also be used to notify the system that this block is free to use. Regardless of the ISR implementation, it should include the following basic procedures:

- Set all RY/BY# masks in the Ready-Busy Mask Register. This prevents additional interrupts within the ISR (i.e. prevent re-entrant interrupt). Keep track of mask setup to reinstate before ISR exit.

- Check the queue of erasing devices and read the Ready-Busy Status Register to determine which device completed the operation.

- 3. Service the erased block(s). Even though one erased block generated the interrupt, more blocks may have completed erasing at this point.

- 4. Clear RACK in the Ready-Busy Mode Register.

- 5. Before exiting the ISR, reset the mask. This "catches" devices that went ready during the ISR and will cause a re-entrant ISR. However, at this point in the ISR, this will not affect system or software integrity.

#### **WRITE-PROTECTION REGISTER**

The Series 2 Card contains a PCMCIA-defined, hard-wired Card Information Structure (CIS) accessed in the Attribute Memory Plane. This data structure provides fundamental, unchanging information pertaining to the card. It includes card size, type of components, access speed, etc. Situations exist where the user needs to include custom-format information, such as card partitioning and operating system specific information.

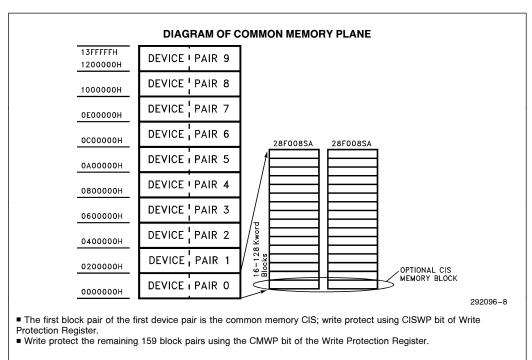

Figure 16. The WRITE PROTECT REGISTER Blocks Writes to the Two Sections of the Common Memory Plane

This information can be loaded in the Common Memory CIS during card format (refer to Figure 16). Typically, after writing this information, it would rarely change. The Series 2 Card provides a means of locking this area of memory, as well as the remainder of the Common Memory array with the Write Protection Register (Figure 17). The Write Protection Register has an advantage over the mechanical write protect switch in that it allows software to control user write access to the card's data (the mechanical switch can be easily switched off enabling card writes). For example, a pen-based system may use this feature to protect its read-only operating system stored within the Series 2 Card.

The CIS Write Protect Bit (CISWP, bit 0) prevents writes to the Common Memory CIS blocks. When software determines that this block of memory contains valid, custom-format information (contains PCMCIA tuple data structure), the CISWP Bit could be set to prevent accidental data corruption by another application. Note that if an End-User format utility is provided, this software must be careful not to destroy the custom format information which could be accessed if the CISWP Bit was deactivated. The Common Memory Write Protect Bit (CMWP, bit 1) prevents writes to the remainder of the Common Memory Plane (i.e. minus the Common Memory CIS blocks). To "software"-write-protect the entire Common Memory Plane, both bits must be set.

#### Write Protection Register Performance Enhancement Register

| ADDRESS | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 4104H   |       |       | RESE  | RVED  |       |       | CMWP  | CISWP |

- CISWP = Common Memory CIS Write Protect

- CMWP = Common Memory Write Protect

- "1" = Write Protected

Figure 17. Provides a Software Implementation of the Write Protect Switch

#### **CARD STATUS REGISTER**

#### **Performance Enhancement Register**

This (Read-Only) register provides quick access to generalized conditions within the Series 2 Card (Figure 18). It provides a shorthand method for checking the following functions:

- Ready/Busy Status

- Ready/Busy Masking

- Deep-Sleep Modes

- Setting of Mechanical Write-Protect Switch

- Software Write Protect Status

- Soft Reset Status

Where the RY/BY# Bit (bit 0, Card Status Register) displays the operation status of the cumulative devices within the card, the Ready-Busy Status Registers reflects the status of each individual device. Bit 0 (RDY/ BSY#) mirrors the card's RDY/BSY# (Ready/Busy) output pin, also reflecting any Ready/Busy masking conditions. Two circumstances warrant the use of this bit: 1) When the hardware interrupt triggered by the RDY/BSY# pin produces an unacceptably long latency period, this bit should be software polled instead to increase performance; 2) When multiple devices have data-write/block-erase operations in progress, reading this cumulative Ready/Busy status will be quicker than reading multiple status registers within each device. However, when the application requires immediate access to each device as it finishes an operation, individual Device Status Registers or the card's Ready-Busy Status Register must be used.

# Card Status Register Performance Enhancement Register

| ADDRESS | BIT 7 | BIT 6 | BIT 5  | BIT 4 | BIT 3  | BIT 2 | BIT 1 | BIT 0    |

|---------|-------|-------|--------|-------|--------|-------|-------|----------|

| 4100H   | ADM   | ADS   | SRESET | CMWP  | PWRDWN | CISWP | WP    | RDY/BSY# |

- RDY/BSY# = Reflects PCMCIA interface RDY/BSY# pin, 0 = busy

- WP = Mechanical Write Protect Switch, 0 = off

- CISWP = Common Memory CIS Write Protect, 0 = off

- RP = Reset-Powerdown Reflects RP in Global Reset-Power Down Reg, 1 = Power Off

- CMWP = Common Mode Write Protect, 0 = Off

- SRESET = Soft Reset Reflects SRESET in SOFT RESET Reg, 1 = Soft Reset

- ADS = Any Device Pair Powered Down, OR'd Condition of Sleep Control Reg, 1 = Power Off

- ADM = Any Device Masked, OR'd Condition of Ready-Busy Mask Reg, 1 = Masked

Figure 18. Provides Generalized Card and Device Information

Bit 1 reflects the card's mechanical switch position (1 = Write Protected). This switch disables any writes to the card. Two software strategies can be implemented for this bit: 1) Assume the card's Write-Protect switch is off. Attempt to write to the card and only check the Write-Protect status if the data-write fails (which it will if the switch is on); 2) Check the switch first to avoid the possibility of failing a data-write. The choice depends on the application.

Bits 2 (CISWP = Common Memory CIS) and 4 (CMWP = Common Memory Write Protect) are direct (Read Only) inputs from the Write-Protect Register. These bits should be checked in a manner similar to that for Bit 1 (WP). For more detail refer to the Write-Protection Register section.

The RP Bit (bit 3) provides a (Read Only) version of the RP Bit in the Global Reset-Powerdown Register (1 = RP). Only the Attribute Memory Plane is available with the Reset-Powerdown feature enabled, allowing access to the Component Management Registers.

The SRESET Bit (bit 5) provides a (Read-Only) version of the SRESET Bit in the **Soft Reset Register** (1 = Locked in soft reset state).

#### **SUMMARY**

The Series 2 Flash Memory Card delivers the hardware capabilities required for implementing a solid-state storage device. Software engineers will find the features of this card both flexible and powerful when coupled with flash-optimized filing systems, such as Flash File System from Microsoft. This application note has discussed the various methods of using the Component Management Registers to facilitate designs incorporating the SERIES 2 card.

- PCMCIA-Defined Registers provide generalized assistance for memory card interfacing.

- Performance Enhancement Registers boost software control over the card's internal flash memory devices.

#### **GLOSSARY**

Attribute Plane: Memory plane within the card selected by pulling the REG# pin low. This random access memory contains the CIS and Component Management Registers.

**Block-Erase:** Erasing sections of a single flash memory device.

**Bulk-Erase:** Erasing the entire flash device simultaneously.

Common Memory: The memory card's main memory array.

Common Memory-Card Information Structure: The first block pair of the first device pair. Useful for storing custom format information, such as partitioning of the card.

Component Management Registers (CMR): Memory-mapped I/O registers used to control device-level functions.

**Deep-Sleep Mode:** A special very low power mode useful for saving power when not accessing the flash memory components.

**Device-Pair:** Arrangement of the 8-bit 28F008SA devices in the SERIES 2 card in a word-wide manner.

Hardwired Card Information Structure (CIS): Embedded into the Attribute Memory Plane to describe

non-changing information about the SERIES 2 Card (i.e. density, speed).

Personal Computer Memory Card International Association (PCMCIA): The organization formed to promote interchangeability of IC cards by providing a standardized mechanical, electrical and metaformat interface.

Performance Enhancement Registers: Memory-Mapped I/O registers included by Intel in the Series 2 Card to boost performance by providing software control of the internal 28F008SA functions.

**Ready/Busy:** Indicator used to determine when a datawrite or block-erase operation has completed. Symbolized by RY/BY# for the 28F008SA and RSY/BSY# at the Series 2 Card interface.

Status Register: A register internal to a 28F008SA FlashFile<sup>TM</sup> Memory device used to determine write and erase operation status.

#### **RELATED DOCUMENTS**

28F008SA, 8 Megabit, FlashFile™ Memory Data Sheet

Series 2 Flash Memory Card Data Sheet 82365SL, PC Card Interface Controller Data Sheet PCMCIA PC Card Standard Release 2.0