## Quatro-960 PCI Add-In Card Evaluation Platform

- Reconfigurable to Allow

Benchmarking of i960<sup>®</sup> Processors

- Up to 40 MHz Local Bus Operation

- Uses V<sup>3</sup> Corporation's V96xPBC i960 CPU-to-PCI Bridge Controller

- Up to 2 Megabytes of Wait State Configurable SRAM

- Up to 2 Megabytes of Ultra High-Performance Synchronous SRAM

- MON960 in On-Board ROM With Serial Host Communications

- 96-Pin Expansion Header For Custom Hardware Prototyping

- Includes Schematics and Documentation

- PCI Based or Stand Alone Operation

- Ideal For Intelligent Add-in Card Prototyping

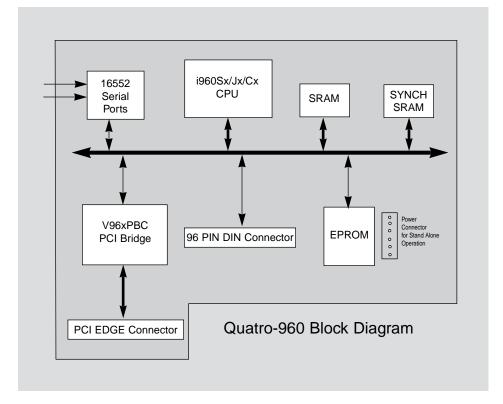

The Quatro-960 add-in card provides embedded system designers a ready-made solution for i960 processor based PCI design. Quatro-960 is designed to support the i960 Sx, Jx and i960 Cx processor; all on the same PCI-standard form factor card. The heart of the Quatro-960 card is the V96xPBC family i960 processor to PCI Bridge component.

The Quatro-960 also includes two types of RAM memory: Standard SRAM and ultra high-performance synchronous SRAM. V<sup>3</sup> chose to use SRAM for this board to allow customers complete control over wait state profiles, as well as to allow prototyping of very high-performance designs. DRAM can be added via an optional daughtercard.

Quatro-960 is designed with expansion and prototyping in mind. A 96-pin DIN connector is provided that includes all necessary local bus signals. MON960, the Intel standard monitor/debugger, comes standard in ROM. MON960 has been customized to fully initialize the V96xPBC. Example PCI programs are provided along with full source code listings.

The documentation kit for Quatro-960 includes schematics, PAL equations, example code (both C and assembly), data sheets and manuals for all devices.

PROCESSORS SUPPORTED: i960 Sx, Jx, Cx Processors

AVAILABILITY:

September 1995

V<sup>3</sup> Corporation

2348 Walsh Ave., Suite G

Santa Clara, CA 95051

Phone: (408) 988-1050

FAX: (408) 988-2601

Att: Marty Allen

For international contacts see Appendix B.